© 1973 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

CAMAC CRATE CONTROLLER FOR A SERIAL CONTROL SYSTEM

E. J. Barsotti National Accelerator Laboratory\* Batavia, Illinois

## Introduction

Two years ago the Laboratory was faced with the problem of deciding what type of control system hardware should be used in the Neutrino, Meson, and Proton experimental areas. Realizing that scientists from all over the world would be conducting experiments in these beam lines the Laboratory chose an international standard, CAMAC, as its hardware interface to controlled devices. Because of long distances between control stations a serial control system was necessary. The first attempt at serializing CAMAC was done throughout the two mile long Neutrino beam line. A serial branch driver was designed to interface to commercially available CAMAC type A crate controllers. Due to excessive costs and additional system requirements, another serial system was designed for the Meson and Proton experimental beam lines. The serial crate controller used in this system not only replaces the serial branch driver and type A controller but has two additional features, block transfer and multi-crate addressing capabilities.

## System Configuration

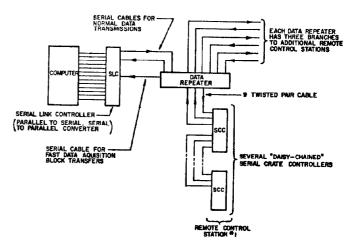

A block diagram of the system using serial crate controllers is given in Figure 1. A maximum of four output data transfers from a mini-computer to the serial link controller are required to load a seventy bit serial word. The serial word is then transmitted thru data repeaters to all serial crate controllers with only the addressed controller returning a thirty-five bit word to the link controller. Transmission between control stations is via bipolar transfer-coupled 1 MHz pulses whereas nine balanced driver/receiver pairs are used for transmitting signals between "daisy-chained" controllers. Each data repeater has three additional input and outpuc pairs of ports for "branching" to additional remote control stations.

#### Serial Crate Controller Specifications

Read and write operations thru an addressed serial crate controller from or to a CAMAC module are performed as follows. The first thirty-five bits of the serial word contain the controller's address, the command to be performed, and odd parity, control, and timing bits. Because the system is synchronized to the serial link controller's internal clock, the serial word is always seventy bits long. The last thirty-five bits contain data during a write command and timing bits for five status return bits. The crate controller returns the transmitted data and status bits during a write operation and read data and status bits during a read operation. Neglecting cable propagation delays and software overhead time, an operation to a crate controller requires seventy microseconds.

If a parity error is detected on the address-command portion of the incoming word, no return word is transmitted. If during a write operation a parity error is detected on the data, a status bit in the return word is set.

The serial crate controller contains all the features of a CAMAC A-1 crate controller making it compatible with commercially available CAMAC modules. When power is applied to the serial controller a CAMAC "initialize" command is generated which sets the controller and all modules in the same crate to a predefined initial state.

Multi-crate commands are performed by setting a bit in the serial word allowing the serial system to address a pre-determined block of crates with one output transmission. Patching permits several different combinations of crates to be addressed by a series of multi-crate commands.

An additional feature of the serial crate controller is its ability to generate block transfers. Such things as digitized analog data and scalers read using this mode of operation result in less software overhead and time savings by factors of five to ten. Dataway cycles required for block transfer data occur only when a seventy bit word is not being transmitted through a crate, thus this mode does not interfere with the operation of the normal serial system in any way.

To initiate a block transfer a register in the crate controller is loaded with a CAMAC read function code  $(F_{\rm X})$  , an initial slot  $({\rm N}_{\rm i})$  , and a final slot  $({\rm N}_{\rm f})$  . Dataway read cycles are then generated starting with a command using the loaded function code, initial slot, and subaddress zero. Each read cycle results in the crate controller transmitting a twentynine bit 1 MHz serial word. The serial word contains twenty-four data bits, end of module and end of block bits, and the Q or X response from the module. One patchable option increments the subaddress until either a no Q(X)response is received from the addressed module or the maximum subaddress, A15 is reached. The module slot is then incremented and the process repeated until the final slot is operated or. The other option "rolls over" the subaddress, not incrementing the slot until a no Q(X) is received. The command sequences and returned status bits for the two modes of operation as described are given on the following page.

<sup>\*</sup> Operated by Universities Research Association, Inc., under contract with the U. S. Atomic Energy Commission.

Normal Mode

|                                                | Q        | End of     | End of           |

|------------------------------------------------|----------|------------|------------------|

| Command                                        | Response | Module Bit | <u>Block</u> Bit |

| F <sub>x</sub> A <sub>C</sub> N <sub>i</sub>   | 1        | 0          | 0                |

| FxAlNi                                         | 1        | 0          | 0                |

| $F_{x}^{A_{2}N_{i}}$                           | 1        | 0          | 0                |

| •                                              | •        | •          |                  |

| •                                              | •        | •          | •                |

| •                                              | •        | •          | •                |

| $F_{x^{A_{15}N_{i}}}$                          | 1        | 1          | 0                |

| $F_{x}^{A}0^{N}i+1$                            | 1        | 0          | 0                |

| •                                              | •        | •          | •                |

| •                                              | •        | •          | •                |

| •                                              | •        | •          | •                |

| <sup>F</sup> x <sup>A</sup> y <sup>N</sup> i+1 | 0        | 1          | 0                |

| $F_{x}^{A}0^{N}i+2$                            | l        | 0          | 0                |

| •                                              | •        | •          |                  |

| •                                              | •        | •          | •                |

| •                                              | •        | •          | •                |

| <sup>F</sup> x <sup>A</sup> z <sup>N</sup> f   | 0        | 1          | 1                |

# Subaddress Rollover Mode

| Command                                        | Q<br>Response | End of<br>Module Bit | End of<br><u>Block</u> Bit |

|------------------------------------------------|---------------|----------------------|----------------------------|

| F <sub>x</sub> A <sub>0</sub> N <sub>i</sub>   | 1             | 0                    | 0                          |

| <sup>F</sup> x <sup>A</sup> 1 <sup>N</sup> i   | 1             | 0                    | 0                          |

| F <sub>x</sub> <sup>A</sup> 2 <sup>N</sup> i   | 1             | 0                    | 0                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| <sup>F</sup> x <sup>A</sup> 15 <sup>N</sup> i  | 1             | 0                    | 0                          |

| F <sub>x</sub> A <sub>0</sub> Ni               | 1             | 0                    | 0                          |

| <sup>F</sup> x <sup>A</sup> l <sup>N</sup> i   | 1             | 0                    | 0                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| F A Ni                                         | 0             | 1                    | 0                          |

| $F_{x}A_{0}N_{i+1}$                            | 1             | 0                    | 0                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| F <sub>x</sub> A <sub>y</sub> N <sub>i+1</sub> | 0             | 1                    | 0                          |

| F <sub>x</sub> A <sub>0</sub> N <sub>i+1</sub> | 1             | 0                    | 0                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| •                                              | •             | •                    | •                          |

| Fx <sup>A</sup> z <sup>F</sup> f               | 0             | l                    | 1                          |

All block transfer data enters the computer via its interrupt controlled fast access port.

# Cost Savings and System Maintenance/Testing

Neglecting the costs of common hardware a cost comparison between a system using serial crate controllers and one using serial branch drivers, Type A controllers, branch terminators, etc. shows that the former results in savings from 73% for a one crate to 65% for a seven crate local control station.

The serial crate controller consists of three single width printed circuit board modules for easy testing and maintenance interconnected thru rear connectors. Unlike the parallel branch highway system, interconnections are minimized by transmitting the serial word thru each serial crate controller.

The upper CAMAC crate in Figure 2 has a serial crate controller in its three rightmost slots, 23 thru 25. The bottom connector of the module in slot 23 is used when "daisychaining" controllers at a local control station. The module's top connector is used to interconnect the controller with the normal data and block transfer data repeaters in slots 22 and 21 respectively. The bottom crate contains much of the equipment used in system maintenance and testing.

# Acknowledgments

I would like to express my appreciation to Rod Wischermann for all the assistance he gave me during the development of the serial crate controller.

Figure 1.

Figure 2.