© 1973 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

COMPUTER CONTROL OF THE OAK RIDGE ISOCHRONOUS CYCLOTRON\*

C. A. Ludemann, J. M. Domaschko, S. W. Mosko and K. Hagemann<sup>+</sup> Oak Ridge National Laboratory, Oak Ridge, Tennessee 37830

## Summary

The controls of the Oak Ridge Isochronous Cyclotron are being interfaced to a computer system. The initial implementation of the system is designed to reduce the time for setting up the cyclotron between experiments and to closely monitor the operation of the accelerator's power supplies. The system will be expanded to include the monitoring and control of the RF, beam-line, and vacuum systems. Later, diagnostic devices will be interfaced so that beam quality and intensity may be optimized. The operator communicates with the cyclotron via a CRT interactive display and a control console containing reassignable function keys and LED readout devices. The computer is a Modular Computer Systems MCS III/5. Operation data and programs for controlling the cyclotron are stored on disc and magnetic tape libraries.

## Introduction

Installation of a computer control system is underway at the Oak Ridge Isochronous Cyclotron (ORIC). Some objectives of this program are improved time utilization through faster setup, better performance through the ability to control many key parameters simultaneously and efficient bookkceping for operations information. Since ORIC is a continuously operating facility with an extremely complex control system, the implementation of new control techniques is necessarily a gradual process. A control computer is already installed. Interfacing the computer to ORIC's magnet power supplies is the first project underway. Simultaneously, an interface between the computer and an existing data acquisition system is being developed. Some other problems to be considered in the future are automatic setup of the RF system, and the ion sources. Long range plans include automatic beam optimization.

#### Control Computer and Peripherals

A Modular Computer Systems MCS III/5 computer with a 24K, 16-bit word memory was acquired in October, 1972. The peripherals include an ASR-33 teletype keyboard/printer, a high speed serial printer, high speed paper tape reader and punch, a magnetic tape unit, a 1.2 million word disc storage device, a card reader, a CRT alphanumeric and graphic display with semiconductor memory and keyboard, a digital I/O subsystem, and an 80-channel, 11-bit ADC system.

Standard software includes a sophisticated realtime multiprogramming system with foreground, middleground and background capability. It is task oriented and allows real-time tasks to be concurrently executed on up to 256 unique priority levels. A large assembler instruction set includes word, byte and bit manipulation. A FORTRAN IV compiler is also included.

#### Operator-Computer Interface

Operator-computer interfacing is via the CRT alphanumeric and graphic display and keyboard, a panel of approximatley 20 reassignable pushbuttons, and LED displays.

In order to setup a run, the cyclotron operator picks a set of parameters from a library of previous run parameters via a menu on the CRT screen. The power supplies are automatically switched to appropriate loads and polarities and run up to the listed settings. The operator then assigns pushbuttons to various power supplies as needed for fine tuning the cyclotron. Both fast and slow adjustment rates are available with the pushbuttons. The computer monitors power supply response and keeps track of power supply settings. If it detects abnormal power supply operation the computer alerts the operator. At the operator's option, the computer stores new run information in its run library. Vacuum and cooling system configuration and performance information is available for display on the CRT.

### Typical Power Supply Controller/Monitor

The typical ORIC power supply requires control resolution and stability to within 1 pp 4000. It is controlled by an analog reference signal and may be monitored via a signal generated across a 100 mV full scale shunt. A few power supplies such as on the main field and the 153° beam analyzing magnet require control to within 1 pp 65,000. All ORIC power supplies are electrically isolated from one another and from building ground.

A computer controlled monitoring system for ORIC is required to resolve errors in power supply regulation of the order of 0.1% at frequencies to 360~Hz and it must also be able to detect power supply oscillation at several kHz.

The original control system has individual voltage reference sources with potentiometers. Early computer control systems provided reference voltages via programmable stepping motor driven potentiometers and/ or relay driven ladder networks. More recently, with declining costs and increasing variety in microcircuits, it has become economical to use DAC's as reference sources and to include a monitoring system within the power supply controller.

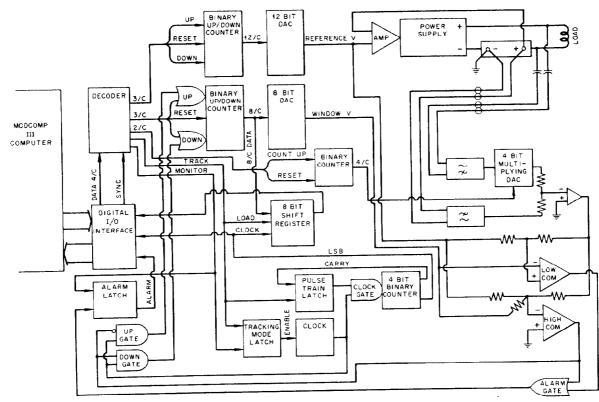

Figure 1 is a simplified schematic of a typical ORIC power supply controller/monitor (C/M). The C/M generates a reference signal which controls the power supply. The power supply output is compared to the reference by comparators which generate binary error information. The reference and the comparator offsets are derived from DAC's. All I/O data is converted into digital form and transmitted between the C/M and the computer I/O interface through optical couplings. The input data to the C/M is a 4 bit instruction word and a sync pulse. The various instructions are listed in Table 1. Each instruction results in a pulse being channeled by the decoder to the appropriate part of the C/M.

Power supply performance is best measured on a precision shunt in the output circuit. Unfortunately, due to low signal levels and extremely noisy environment,

<sup>\*</sup>Research sponsored by the U.S. Atomic Energy Commission under contract with Union Carbide Corp.

<sup>&</sup>quot;Visiting scientist from Niels Bohr Institute, Denmark.

ORNL-0WG 73-2197

Fig. 1. Schematic diagram of the typical power supply controller/monitor.

| Instruction Word | Operation                   |

|------------------|-----------------------------|

| 0000             | Reference DAC up one step   |

| 0001             | Reference DAC down one step |

| 0010             | Reference DAC reset         |

| 0011             | Window DAC up one step      |

| 0100             | Window DAC down one step    |

| 0101             | Window DAC reset            |

| 0110             | Multiplying DAC up one step |

| 0111             | Multiplying DAC reset       |

| 1000             | Monitor                     |

| 1001             | Track                       |

Table 1. C/M Control Instructions

bandwidth is limited to a few Hz. Consequently, a separate high level signal is taken from across the load for high frequency information. The two signals are fed to the comparator circuits by low and high pass filters respectively. The amplitude of the high frequency signal can be varied via a 4 bit multiplying DAC.

During normal operation, a monitoring mode is set. The monitor command is given to reset the alarm latch. The 8-bit DAC generates comparator offset levels which define a window within which the power supply is expected to operate. If the power supply error signal deviates from within the window, the appropriate comparator trips the alarm latch and the CPU is alerted through an interrupt. The cyclotron operator is warned via audio signal and CRT display. Information on ripple frequency and amplitude may be obtained by repeatedly giving the monitor command and sampling the alarm latch while varying sampling rate and window width.

A tracking mode is provided in which the power supply error signal waveform is digitized. When the track command is given a latch is set which enables a 2 MHz clock. The clock pulses are input to the up gate and down gate with the output of the high comparator determining which gate shall be clocked. The clock pulse is then routed to drive the up/down counter of the 8-bit DAC and forces the comparator summing point a step toward ground potential. When the summing point reaches ground potential, the up/ down counter digitally follows the error signal within ± 1 LSB. The track command pulse also initiates transfer of the 8-bit DAC counter setting to the computer. The decoder pulse loads the counter reading into a shift register. Upon termination of this pulse the pulse train latch is set which opens the clock gate and clocks the 4-bit binary counter. The LSB of the 4-bit binary counter is used to clock the 8-bit shift register contents into another shift register within the digital I/O interface. When the 4-bit binary counter reaches full scale, the carry pulse resets the pulse train latch stopping the pulse train to the 8-bit shift register with a total of 8 pulses.

The 4-bit multiplying DAC allows computer adjustment of ripple tracking resolution. It also provides a means for turning off the ripple input into the summing points when a power supply has periodic spikes which may be temporarily "tolerated" without tying up CPU time.

The C/M tracking mode has a bandwidth of 4 KHz for sinusoidal waveforms and sampling rates of up to 40,000/sec are possible. Power supply error signals are typically monitored within a range of 0.05% to 0.5% of full output.

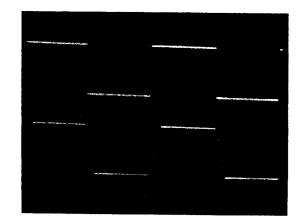

Figure 2 is an oscilloscope photograph of the C/M tracking response to a 1 volt, 1 kHz square wave input

signal. The upper signal is taken from the AC input. The lower signal is taken from the output of the 8-bit DAC and ranges over 120 steps of its up/down counter. The time base is 0.2 mS/cm.

All C/M's will be multiplexed into a control module within the digital I/O interface using a dataway-station line - "look at me" scheme similar to that of the CAMAC standard.

# Data Acquisition System

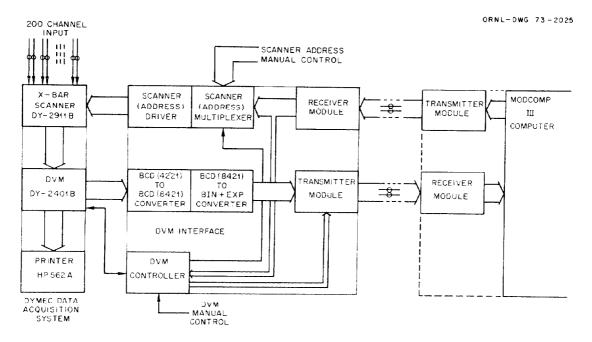

A "DYMEC" data acquisition system consisting of a digital voltmeter (DVM) with a crossbar scanner is used for slower precision monitoring of ORIC's power supplies. 200 data channels are available with a maximum resolution of 3 pp  $10^6$ . A bidirectional interface links the data acquisition system to the computer. In Figure 3 a schematic diagram of the interface is shown. A 16-bit word from the computer is required to initiate a data recording cycle. Depending on the content of the most significant bit the word is interpreted as an "entry command" which modifies the status and function of the system, or a "control command" which requests a single data transfer or a sequential block of data.

After transmission of such a command the computer is released for other purposes. A sequence controller in the interface starts the DVM after the crossbar scanner has advanced and then waits for a data ready signal from the DVM. The BCD(42'21) output of the DVM is converted to BCD(8421) code which is finally converted to a 20 bit binary fraction and a 4 bit binary exponent. The two step conversion provides the interface with a general structure. After conversion is completed, the sequence controller generates an interrupt, and the data are transmitted to the CPU. Three 16-bit words of binary input are required on the I/O bus including two words of data one word of status information. A computer initiated manual operation mode is available which permits manual use of the data acquisition system subject to a CPU generated interrupt.

Fig. 2. Tracking response of the C/M to a 1 volt, 1 KHz square wave. The lower signal is taken from the C/M window (tracking) DAC output. The time base is 0.2 mS/cm.

## Status of the Control System

The computer and its peripherals are installed and checked out. A prototype power supply controller/ monitor is in operation and has been satisfactorily tested on several power supplies. A full set of C/M modules is under construction. The C/M's are expected to be incorporated into cyclotron control by late April, 1973.

The DVM interface has been constructed and is to be installed shortly. Power supply switching gear is in the planning stage.

Software being developed for C/M and DVM control will be incorporated into a master menu-picking routine which will be the main interface between the operating staff and the control system through the CRT.

Fig. 3. Schematic diagram of the data acquisition system interface.