## LANSCE CONTROL SYSTEM'S 50<sup>TH</sup> ANNIVERSARY\*

## Martin Pieck<sup>#</sup>, Christopher D. Hatch, Jeff O. Hill, Heath A. Watkins, Eric. E Westbrook Los Alamos National Laboratory, Los Alamos, NM 87545 USA

2011

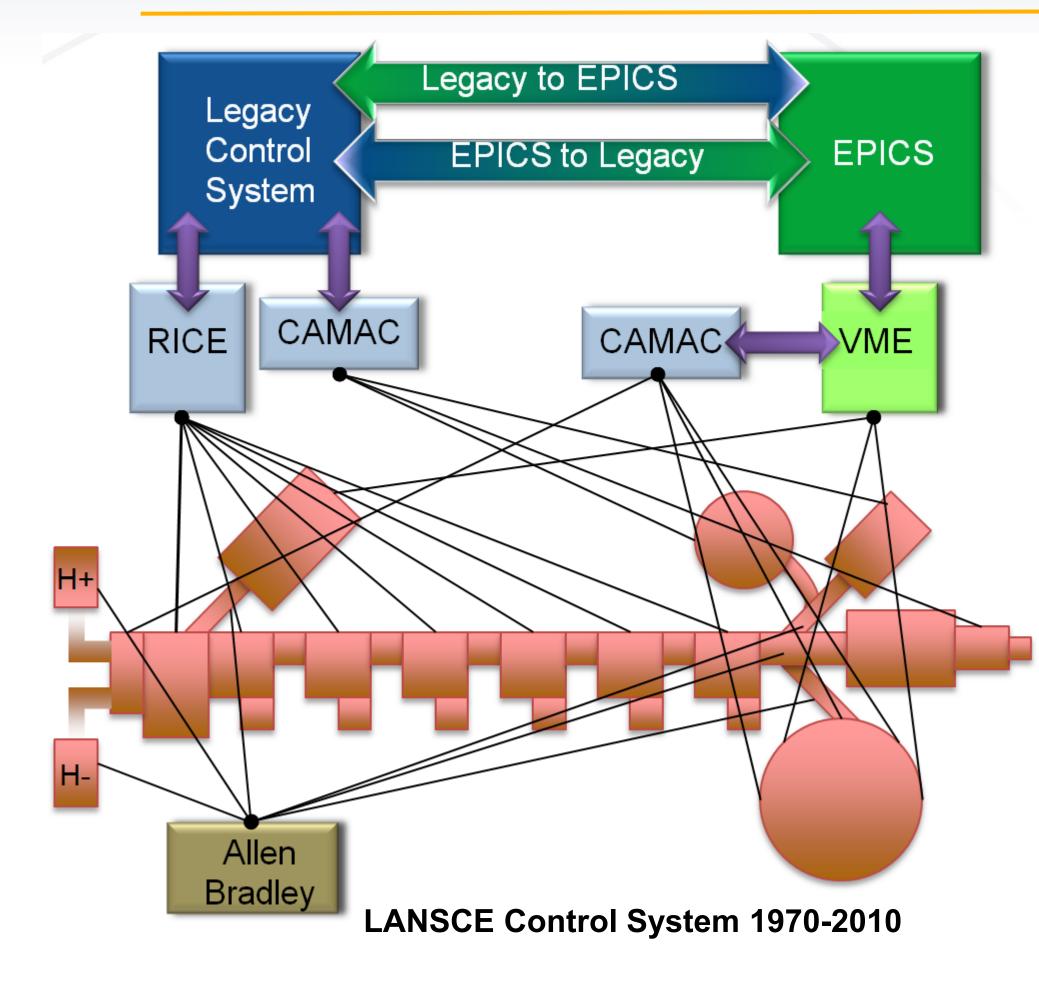

After being almost exactly 50 years in service, the Los Alamos Neutron Science Center (LANSCE) control system has achieved a major milestone – replacing its original and reliable RICE (Remote Instrumentation and Control Equipment) with a modern customized control system. The task of replacing RICE was challenging because of its technology (late 1960's), number of channels (>10,000), unique characteristics (all-modules data takes, timed/flavoured data takes) and that it was designed as an integral part of the whole accelerator. In the paper we discuss the history, RICE integral architecture, upgrade efforts, and the new system providing cutting edge capabilities. The boundary condition was that upgrades only could be implemented during the annual four-month accelerator maintenance outage. This led to a multi-phased project which turned out to be about a 11-year effort.

Fiber Optics Network installed

Industrial I/O (CRIO)

805 MHz Linac (cRIO) Wire Scanner

Master

Timer

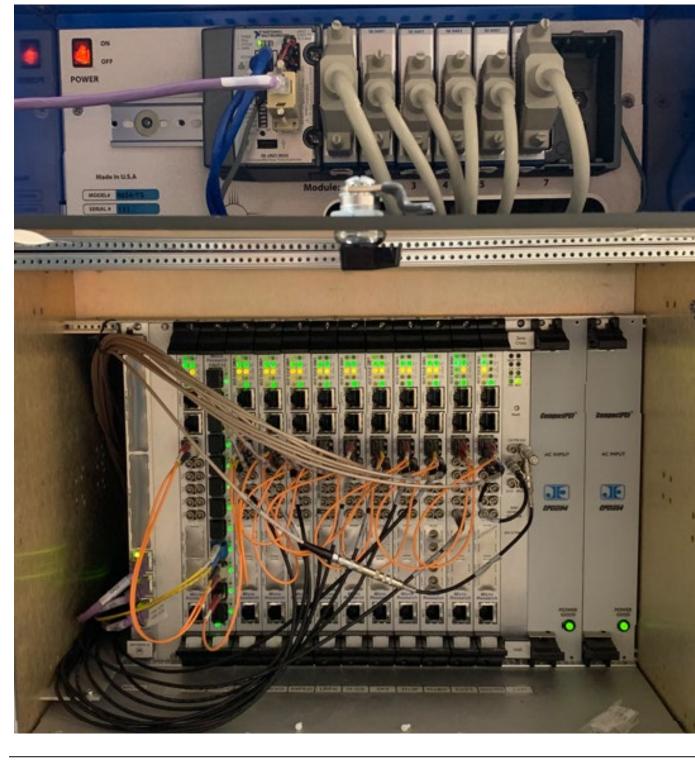

-month accelerator hased project which National Instruments' (NI) compact Remote Input Output (cRIO) provides a wide variety of modules. Third party products complement the NI module product line. A Module Development Kit allows the development of custom modules. The cRIO is a fast and flexible solution with EPICS directly running on the Real Time Controller (RTC) which gives access to all the EPICS tools. The RTC embedded EPICS IOC communicates with a LabVIEW RT program via IvPortDriver or

directly with the FPGA through NI's C-API. Its flexibility through the freedom on how an application is partitioned between the FPGA, LabVIEW RTC, and EPICS. The independently running FPGA, interfacing directly with the cRIO I/O modules keeps running even though the EPICS IOC is rebooted. For our Industrial controls applications, we installed 152 systems, that are mounted in a commercial BiRIO chassis which interfaces to BiRIO interface boards interfacing to field wiring.

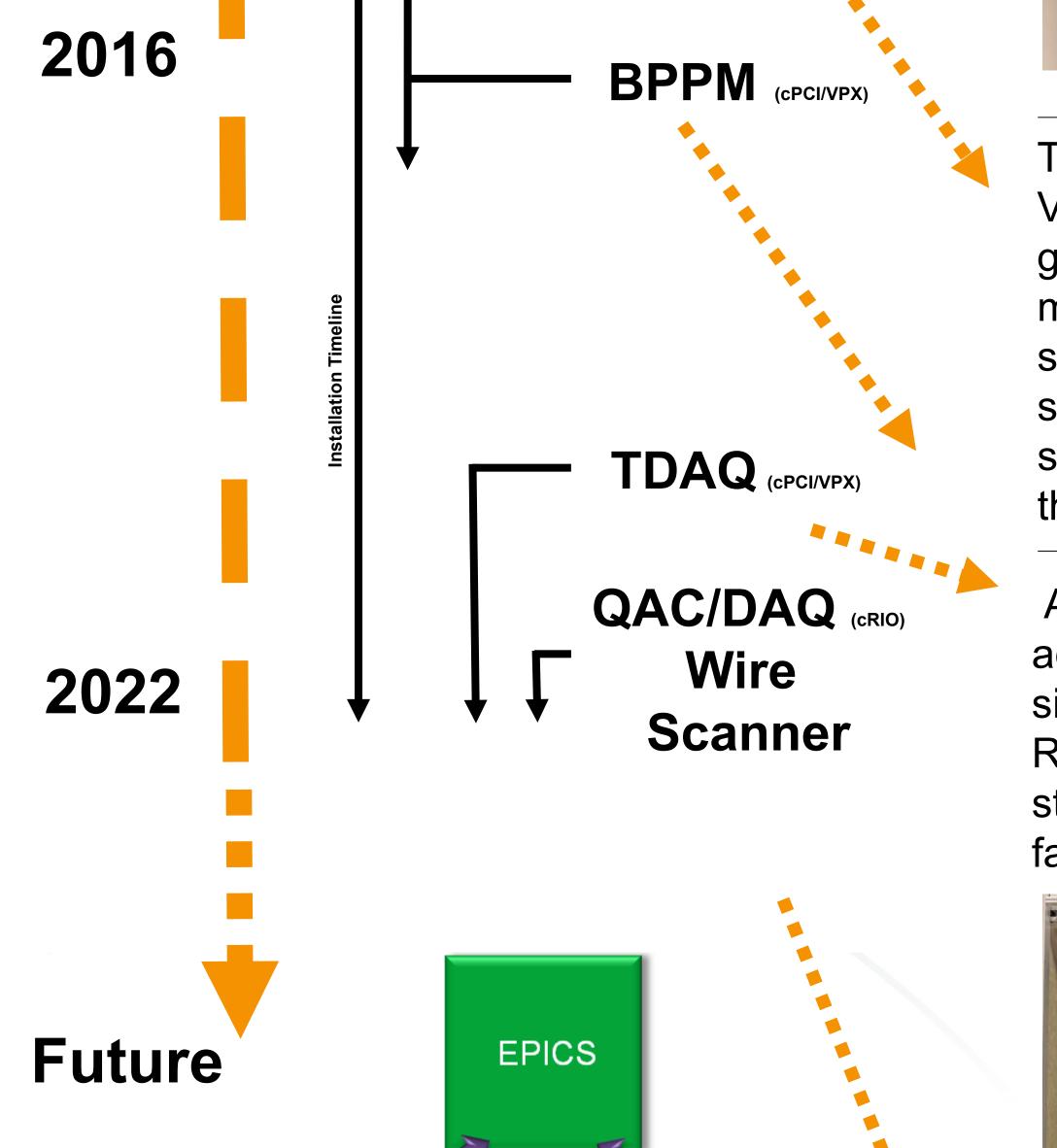

The Wire Scanner (WS) prototype was tested at the end of the 2010 run cycle which paved the way for a complete 32 WS system (actuator, cable plant, and instrumentation chassis) upgrade in the 805 MHz linac between 2011 and 2022. Each chassis is dedicated to one WS and has a Touch Panel Computer (TPC) to provide real-time visual display of wire-scanner operations & access to manual actuator control. We used NI's Module Development Kit to design a specific, commercially unavailable, cRIO Analog Front End (AFE) module.

The new Timing Pattern Generator (TPG) is a dual-redundant system based on a VME-64x crate, a MVME-6100 processor, a set of Micro Research Finland eventgenerator modules, and an AC zero-crossing detector and beam-enable logic module (cRIO system). The cRIO FPGA-based beam enable logic implements specific features: enabling or disabling a beam from the operator consoles, single-shot mode, single-burst mode, continuous-burst mode, burst of bursts mode & cycle stealing. The new TPG is still using the legacy coax cable-based distribution system through a legacy timing replicator until all Timing IOCs are deployed.

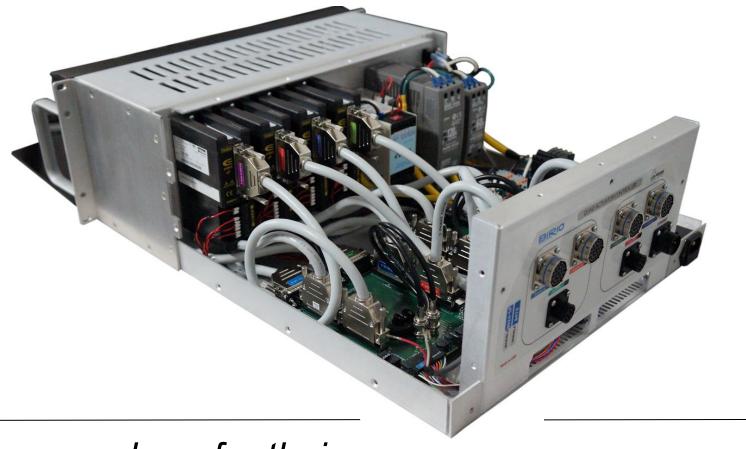

A custom cPCI/VPX architecture in one crate focus on beam-synchronized data acquisition. The cPCI side provides eight 6U cPCI slots for low cost per channel signal conditioning. One slot is usually reserved for a Micro Research Finland Event Receiver for crate timing information. The VPX side modularizes on a new VITA standard high-speed connector, with a switched PCI Express/Ethernet backplane fabric. The crate has six 3U VPX slots. It typically hosts up to five BittWare S43X

FPGA DSP modules with an Altera Stratix IV embedding a NIOS soft-core based EPICS IOC running an RTEMS operating system (OS). For our design one slot is reserved for an PCI Express/Ethernet switch providing network connectivity to all VPX slots via the backplane. The dual (cPCI/VPX) architecture allows the communication between both sides via a PCI Express/Compact PCI Monarch communication bridge. The system is powered by three 250W, plug-in power supplies. The so called TDAQ – timed data acquisition system shares most of its modular software and hardware components with our Beam Phase and Position Monitor (BPPM) system and is therefore simplifying maintenance and spares inventory. 62 TDAQ (2020-22) and 28 BPPM (2012-17) systems were deployed in the linac.

\* This work was supported by the U.S. Department of Energy through the Los Alamos National Laboratory. Los Alamos National Laboratory is operated by Triad National Security, LLC, for the National Nuclear Security Administration of U.S. Department of Energy (Contract No. 89233218CNA000001). # pieck@lanl.gov, Associated Paper: LA-UR-2022-27901

The 52 CAMAC based WSs have been upgraded using a dual chassis cRIO based solution. The a) Quad Actuator motion Controller (QAC) & b) Data Acquisition (DAQ) solution, both having a TPC, can run any type of stepper motor actuator at LANSCE (legacy L-RM, stripper foil, emittance, harp) while providing increased density/cost efficiency for stepper motor devices in congested areas (QAC operates up to four motors, DAQ expandable to 80 channels). Moreover, the system is open loop and closed loop compatible. In 2022, 52 WSs were upgraded to the QAC/DAQ solution.

We would like to recognize previous & current LAMPF-LANSCE controls group members for their dedication to keep RICE running for 50 years. We also would like to thank everyone that contributed to the new control system that enabled RICE's well-deserved retirement in 2022.