# THE DEVELOPMENT OF TIMING CONTROL SYSTEM FOR RFQ

J. Bai, L. Zeng, S. Xiao, T. Xu

Institute of High Energy Physics, CAS, Beijing, 100049, P.R China

### Abstract

In order to meet the need of RFQ accelerator, Timing extension hardware based on VME configuration has been developed. In the future, it will be used in the diagnostics system of CSNS. This paper introduces the function of Timing extension hardware, EPICS driver for Timing extension hardware and MEDM operator interface.

### BACKGROUND

The core research of intense-proton beam accelerator is mainly concentrated in the field of beam loss control. Based on the intense-beam RFQ accelerator [1] which accelerates proton beam of 46mA pulse current to 35MeV at more than 7% duty factor, a beam line has been built. In order to do beam loss control experiment, many devices have been developed, one of which is Timing extension hardware. Timing extension hardware, as an important device in the running of RFQ accelerator, provides high accuracy and high stability timing trigger signals for the whole system. In the future, it will be used in the CSNS (Chinese Spallation Neutron Source).CSNS adopts EPICS [2] (Experimental Physics and Industrial Control System) as its software environment. So it is necessary to develop EPICS driver [3] for timing extension hardware.

# INTRODUCTION OF TIMING EXTENSION HARDWARE

Timing extension hardware uses VME bus of A24 nonpriviledged data access address modifier [6]. It is listed below as fig. 1. Since A24 space is of predicable size 16MB, default window encompassing the full space is always provided. The A24 window is for VME bus address from 0x000000 to 0xffffff, which is usually mapped by VxWorks subroutine sysBusToLocalAdrs to local memory from 0xfa000000 to 0xfaffffff [6].

#define VME\_AM\_STD\_USR\_DATA 0x39 /\* A24, nonpriviledged data access\*/

Figure 1: Address Modifiers of A24 nonpriviledged data access

Timing extension hardware based on VME configuration is not only consistent with RFQ requirement, it but also avoids the disadvantage of original timing control system, achieving parameters remedy on line. When operators need to remedy parameters of original timing control system, they have to stop the accelerator and calculate the parameters according to the request of experiments, and then use dip switch to change the parameters. The whole process will

last almost two hours and affect the efficiency, stability and continuity. Besides, Timing extension hardware based on VME architecture achieves utility of the same hardware to perform different functions by using reconfiguration of the FPGA, which enhances the flexibility of timing extension hardware.

Timing extension hardware has two types of functions [4]. One is providing primary timing signals for RFQ and secondary timing signals which divide frequency of primary timing signals for beam commissioning and RF system. The other is providing delaying or broadening timing signals according to the needs of various devices. In fact, the principle of these two functions is calculating clock signals. For example, primary timing outputs a timing pulse when it calculates the clock signal to the certain amount. Broadening hardware is triggered by timing signal and starts counting program. It will output a TTL pulse with the width of 3us when counting program reaches to the setting value.

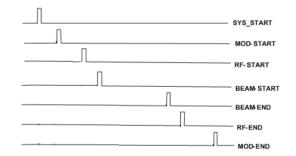

Fig. 2 shows timing signals of RFQ, and the timing extension hardware is shown in Fig. 3.

Figure 3: The timing extension hardware

#### Proceedings of LINAC2012, Tel-Aviv, Israel

| Function                                                       | db                                      |                                                | dbd                                             | Device support                   | Driver<br>support |

|----------------------------------------------------------------|-----------------------------------------|------------------------------------------------|-------------------------------------------------|----------------------------------|-------------------|

| Set primary<br>timing/secondar<br>y timing value<br>Set delay/ |                                         | CHAN): TimingValue:set<br>CARD):\$(CHAN):Value | device(ao,VME_IO,<br>devAoTime,<br>"Time")      | devAoTime{<br><br>Write_ao,<br>} | Write<br>_Val     |

| broaden value                                                  | :set                                    | DTYP                                           |                                                 |                                  |                   |

| Chose clock<br>signal from<br>internal or<br>external          | Time:\$(CARD):Clo                       | •                                              | device(bo,VME_IO,<br>devBoTime,<br>"Time")      | devBoTime{<br><br>Write_bo<br>}  | Write<br>_CSR     |

| Chose logic of<br>primary<br>timing/secondar<br>y timing       | Time:\$(CARD): \$(0                     | CHAN): FimingLogic set                         |                                                 |                                  |                   |

| Chose logic of delay/broaden                                   | DelayOrBroaden:\$(<br>:set              | CARD) \$(CHAN):Logic                           |                                                 |                                  |                   |

| Chose delay or broaden                                         | DelayOrBroaden:\$(<br>:set              | CARD) \$(CHAN):Select                          | •                                               |                                  |                   |

| Read timing register of card                                   | Time:\$(CARD):CS                        | R:read                                         | device(mbbiDirect,VME_IO_<br>devMbbiDirectTime, | devMbbiDirectT<br>ime {          | Read_CS<br>R      |

| Read<br>delay/broaden<br>register of card                      | DelayOr Broaden:\$                      | (CARD):CSR:read                                | "Time")                                         | <br>Read_<br>mbbiDirect<br>}     |                   |

| Read actual<br>primary<br>timing/secondar<br>y timing value    | Time:\$(CARD): \$(0<br>TimingValue:read | CHAN):                                         | device(ai,VME_IO,<br>devAiTime,<br>"Time")      | devAiTime{<br><br>Read_ai,<br>}  | Read_Val          |

| Read actual<br>delay/ broaden<br>value                         | DelayOrBroaden:\$(<br>Value:read        | CARD): \$(CHAN):                               |                                                 |                                  |                   |

| T 1 1 T ' '              | 1 1            | • , ,                 | 1 .       |

|--------------------------|----------------|-----------------------|-----------|

| Table 1: Timing control  | system records | access registers ster | i hvisten |

| rable 1. rinning control | system records | uccess registers step | by step   |

# EPICS DRIVER FOR TIMING CONTROL SYSTEM

The functions of timing extension hardware achieve by single read or write register [5]. Table 1 is provided to give an outline about how records access registers step by step.

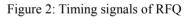

### **OPERATOR INTERFACE**

The operator interface which is under development makes use of MEDM [7] (Motif Editor and Display Manager). With the interface of Timing control system, operator can chose system clock, logic of primary timing and secondary timing, delay or broaden of every channel and logic of every channel. Besides, primary timing, secondary timing, delay or broaden time of each channel can be set through the Interface. Fig. 4 is the operator Interface for Timing control system.

According to the control of interface, timing extension hardware can work normally.

# ACKNOWLEDGEMENTS

The authors would like to thank the CSNS Control Group, Accelerator Center, Institute of High Energy

04 Extreme Beams, Sources and Other Technologies

Physics, CAS to provide the EPICS platform to work on and technical support.

### REFERENCES

- Shinian Fu, Xialing Guan. Development of High Intensity RFQ Proton Accelerator. Beijing: Atomic Energy Science and Technology 2009:1-6

- [2] Argonne National Laboratory. Experimental Physics and Industrial Control System. [Online]Available: http://www.aps.anl.gov/epics/

- [3] Martin R. Kraimer. IOC Application Developer Guide[M]. 1998:1-180

- [4] Shuai Xiao. Lei Zeng. Xian Guo. Taoguang Xu. Timing control system of Intense-beam proton accelerator[C]. Beijing: Nuclear Electronics &Detection Technology 2011: 1-7

- [5] PSI. Writing EPICS Drivers

- [6] WindRiver. WTN-56 Going out on the VME bus

- Kenneth Evans, Jr. MEDM Reference Manual: http://www.aps.anl.gov/epics/EpicsDocumentation/Extensi onsManuals/MEDM/MEDM.html

Figure 4: The operator interface