# EVALUATION OF TIMING AND SYNCHRONIZATION TECHNIQUES ON NI COMPACT-RIO PLATFORMS

O. O. Andreassen, C. Charrondiere, K. Develle, R. Rossel, T. Zilliox CERN, Geneva, Switzerland

WEPHA027

🕒 P 🔘 <mark>S</mark> 2019

## Abstract

Proper clock synchronization between systems is key to successfully integrate data acquisition and control systems in the CERN accelerator domain. This applies to everything from simple diagnostics- to mission critical systems. The internal clock of a National Instruments based CompactRIO (NI-cRIO) system has an accuracy of 40 ppm at 25 °C. In addition, the NI-cRIO onboard FPGA has its own 40 MHz clock with an accuracy of 100 ppm. By default, the NI-cRIO FPGA clock is not synchronized with the controller. For short measurements, this drift is usually negligible, but for continuous data acquisition systems running 24/7, the accumulated error has to be compensated. In this article we show how to correct time drift using protocols such as Network Time Protocol (NTP), Precision Time Protocol (PTP) and White Rabbit (WR) in combination with NI's FPGA TimeKeeper library.

## CHALLENGE.

In cRIO systems, there are up to three timed components: the FPGA, the real-time processor, and hardware timed IO modules such as the GPS or WR module. Each component has a different clock that needs to be synchronized.

A typical RT controller such as the NI cRIO-9035 has a real-time drift of ±40 ppm at 25 °C and the FPGA has a drift of ±100 ppm, which will cause time drifts up to several seconds per day if not synchronized.

In this paper we will focus on Time based synchronization and how White Rabbit can be used to accurately align clocks on both cRIO controllers and FPGA's.

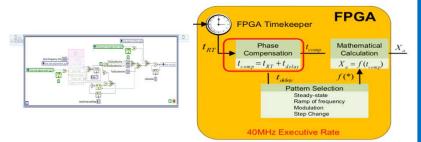

Since the FPGA interface on the cRIO platform doesn't have a built-in way to correct or synchronize the FPGA clock, the developer has to

calculate any clock drift manually. For this purpose, National Instruments has developed a library called FPGA Timekeeper which

takes a timestamp from, for instance, a GPS or WR module as an input

and calculates the real time drift. The library then returns a corrected

time for the FPGA which can be used to timestamp data or align triggers

#### FPGA time keeper

and events

## SNTP synchronisation

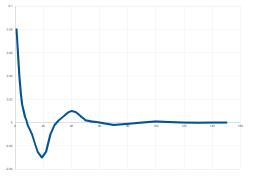

The cRIO controller can be configured to synchronize with both SNTP and NTP through its standard driver set, depending on the controller type. At CERN where the NTP master clocks are in fixed locations and the network routing can be fixed, we have achieved a stable timing accuracy better than 250  $\mu$ s

Difference between NTP and local time at start up

#### EXAMPLE : SEISMIC MONITORING

In 2017, Three seismic measurement stations were installed to monitor the stability of LHC underground experiments. This was done to detect possible disturbances from civil engineering work affecting the accelerators. The stations send their data to a local data base at CERN and in parallel to the Swiss Seismological Service (SED) at the ETH Zürich. SED requires that the raw data arrive to their data server within 10s, sampled at 250 Hz with a 1ms accuracy on every data point, if not the data will be rejected. This means that both the FPGA and the RT controller has to operate with a timing accuracy of less than 1ms.

### Cycle time and acquisition loop

In our system, when configuring a cycle time of 500 µs the real cycle time of the acquisition loop is 500.0025 µs, giving us an error of 2.5 ns. This error can vary both from system to system depending on the FPGA clock, and is affected by external influences such as temperature and humidity, making it necessary to synchronize with an external clock source. After 2000 samples this has accumulated to a 5 µs error.

### CONCLUSION

When designing a measurement or control system, each individual clock in the system has to be considered. As shown, a controller clock with a 40 ppm accuracy can lead to several seconds of drift per day for continuously running applications.

By using tools such as the FPGA time keeper, the cRIO base WR module and NTP we have been able to synchronize and timestamp data on NI-cRIO based systems. This has then allowed successful integration in the CERN accelerator domain and the Swiss Seismological Service.