#### Exceptional service in the national interest

#### Aaron Lombrozo

# Orchestrating a Control System

Timing is Everything

# Shot Control System (Multi-system Synchronization)

# Timing Regimes

| Timing Regime   | os                                       | Response/Jitter range | Hardware/<br>Software                                   | Reliability |

|-----------------|------------------------------------------|-----------------------|---------------------------------------------------------|-------------|

| Non Real-Time   | General Purpose OS                       | 10 ms – 10 s          | PC, Windows,<br>Linux, OSX                              | Low*        |

| Slow Real-Time  | Real-time OS (no optimization)           | 10 ms – 100 ms        | PC, Embedded<br>Controller, WinCE,<br>VxWorks, Linux RT | Medium      |

| Fast Real-Time  | Real-time OS (with optimization/testing) | 10 us – 10 ms         |                                                         | High        |

| FPGA I/O        | Hardware Programming                     | 10 ns – 10 us         | FPGA                                                    | Very High   |

| Delay Generator | Hardware/FPGA                            | 85 ns/100 ps          | Delay Generator**                                       | Very High   |

| Digital circuit | Hardware                                 | 1 ns – 10 ns          | Transistors                                             | Very High   |

<sup>\*</sup>Catastrophic OS-level interruption could occur. May respond late or never.

<sup>\*\*</sup>Minimal logic allowed: ready/not-ready, inhibited/not-inhibited

### System Requirements

- Timing

- High-level shot sequence coordination (slow, flexible)

- Slow charging circuits (reliable, real-time)

- Trigger sources (very fast response)

- Reliability

- Interlocked control of lasers, HV supplies, triggers

- Monitor subsystems for confidence before shot

- Data logging for troubleshooting

- Flexibility

- Custom sequences

- Easily modify timing

- Wide variety of hardware (benchtop, embedded controllers with mixed I/O, subsystems)

- Don't shoot if unexpected problem occurs with any piece of hardware

### **Control Hardware Choices**

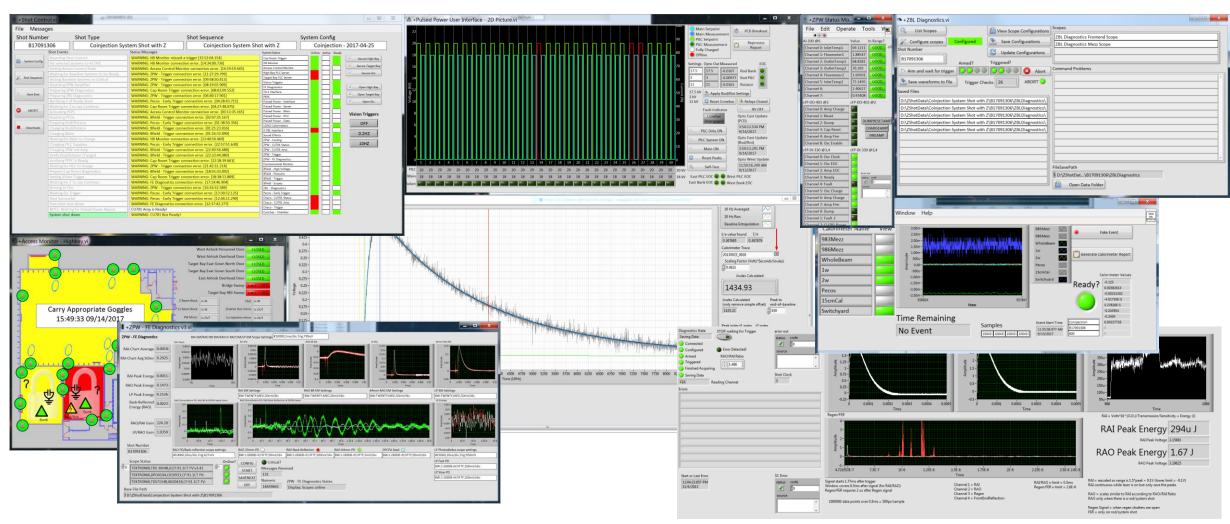

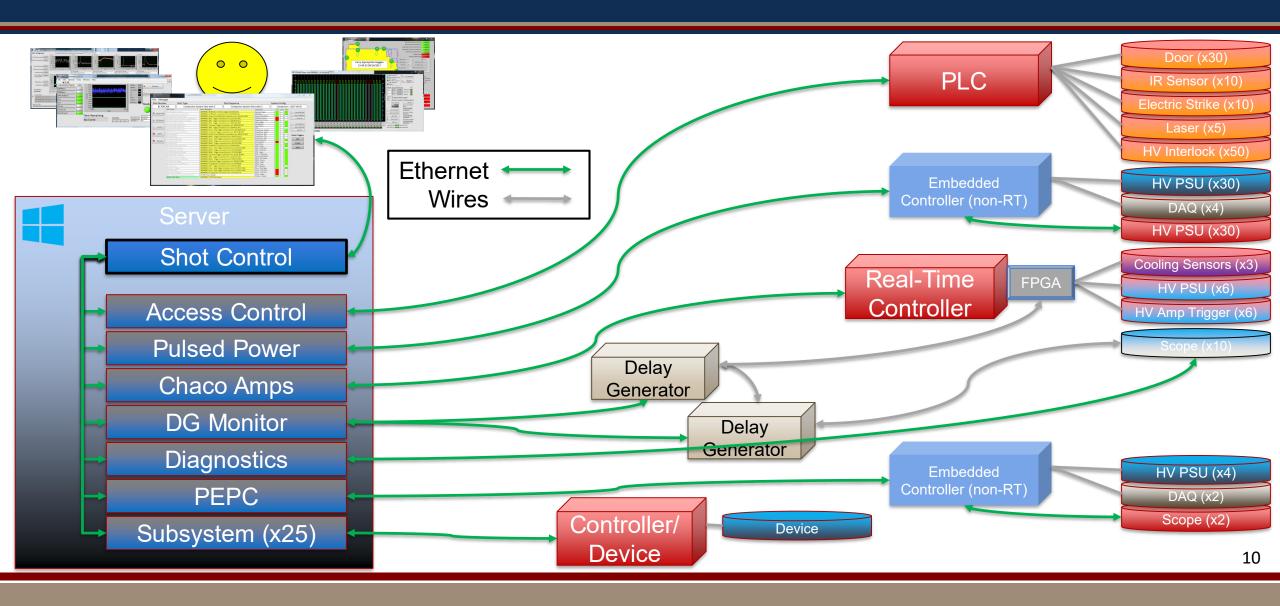

- User Interface

- High-level shot sequence

- Device monitor (DGs, Scopes, HV PSs, DAQs, embedded controllers)

- High/Low-speed RT (10-100 ms)

- Pressure sensors, switches, relays, triggers, slow signals (100 ms), voltage monitors

- FPGA (55 ns 10 us)

- Verify interlocks, verify amp state, and trigger proper flash lamps

- Delay Generators (100 ps)

- Primary trigger chain for initial trigger, amplifiers, laser heads, scopes, cameras, etc.

### Software Architecture

- High level coordinator with custom sequences

- Ensures central control of sequenced events and condition checks

- Easy to troubleshoot, easy to modify

- Low-level subsystems written for specific purposes

- Easier to program for individual tasks without modifying high level coordinator

- Easy to write, easy to test

- Push commands (TCP/IP)

- Fast response, low jitter

- Poll status (NI-PSP)

- Known response/jitter, easy to plan for

## Shot Control Subsystem Diagram

### Summary

- 1. Understand timing requirements for hardware

- 2. Select your ecosystem based on secondary requirements

- Architect your software appropriately to make it easier to satisfy timing, reliability, and troubleshooting requirements

- 4. Keep it simple

## Questions/Discussion/Comments

- Aaron Lombrozo

- Sandia National Laboratories

- aclombr@sandia.gov

Come see our posters on Tuesday to learn more about the Z Facility.