## FPGA-BASED MOTION CONTROL SYSTEM FOR MEDICAL LINEAR ACCELERATOR DEVELOPMENT AT SLRI

R. Rujanakraikarn, P. Koonpong,

## Introduction

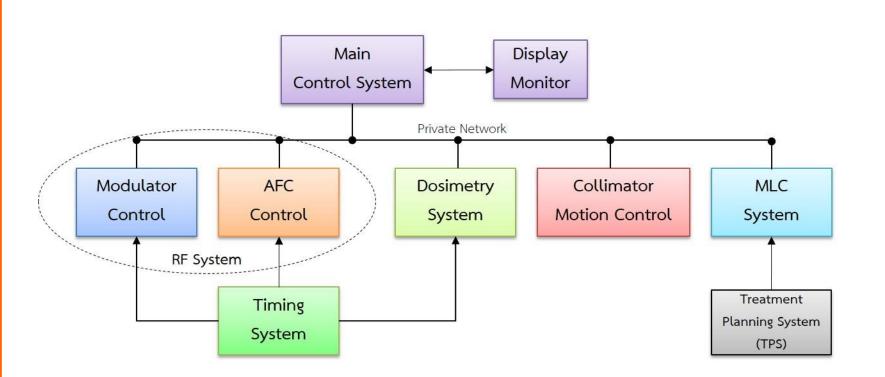

Figure 1: Network diagram of the machine prototype.

Linear accelerator has been widely utilized in radiotherapy machines. An attempt to increase the availability of the low-cost machines has been proposed for the domestic use. Currently, SLRI has developed a prototype of the 6 MeV medical linear accelerator for cancer treatment. Reverse engineering approach has been employed via a donated machine. The prototype consists of a linear accelerating structure of the S-band standing wave type at 2,998 MHz operating frequency, a 3.1 MW magnetron driven by a solid-state modulator, and a hot-cathode electron gun. A drive stand and a gantry of the prototype provide housing for a modulator cabinet and automatic frequency control (AFC) system. The main parts in a linac treatment head consist of an X-ray target, a transmission ionization chamber, and three-stage treatment beam collimators. To confine the shape and size of the radiated beam, the three-stage treatment beam collimators, which are fixed primary collimators, secondary collimators (beam limiting jaws), and a multi-leaf collimator (MLC), are used. A timing system is used to link various subsystems to provide synchronization. Main Control System software is designed to interface with all subsystems. All subsystems are connected to the Main Control System in a private network.

# **Control System Design**

### **Secondary Collimators**

There are two adjustable pairs of jaws, upper collimators (Y-Jaws) and lower collimators (X-Jaws), installed in the treatment head with one pair above the other and at right angles. The jaw openings can be adjusted so that a projected square or rectangular field shape at the target-to-surface distance of the machine ranges from 0x0 cm<sup>2</sup> to 40x40 cm<sup>2</sup>.

Each collimator jaw is driven by a BLDC motor. Traditional H-Bridge circuit is used

#### Feedback and System Integration

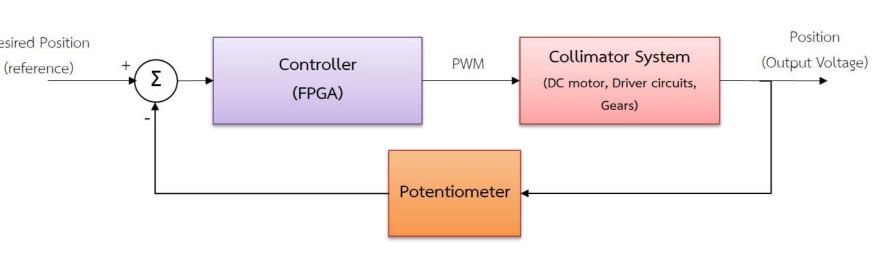

DC motor position control loop is implemented using PI controller. The digital controller is realized using bilinear transformation method in the software part of the control system.

Figure 4: Feedback control loop of each collimator jaw.

to provide appropriate voltage level to control the speed of the motor. The PWM and direction signals are provided by the FPGA. An in-house PWM drive PCB is designed for motor and FPGA interface. A readout potentiometer signals, whose range is from -10 volts to 10 volts, are provided to the FPGA via the PCB.

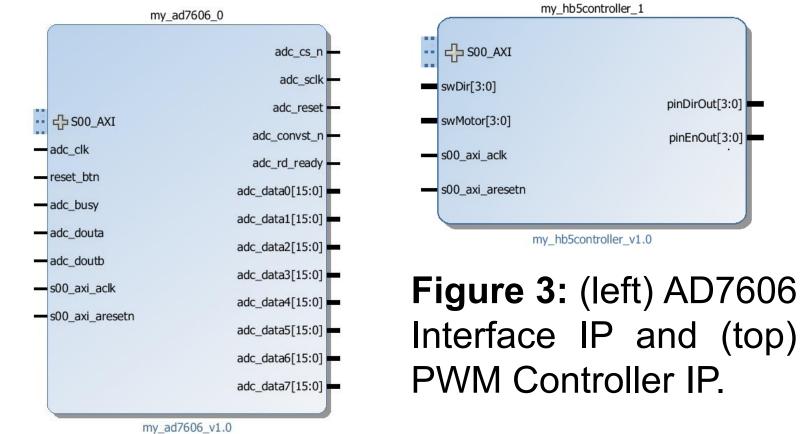

**FPGA** and **ADC**

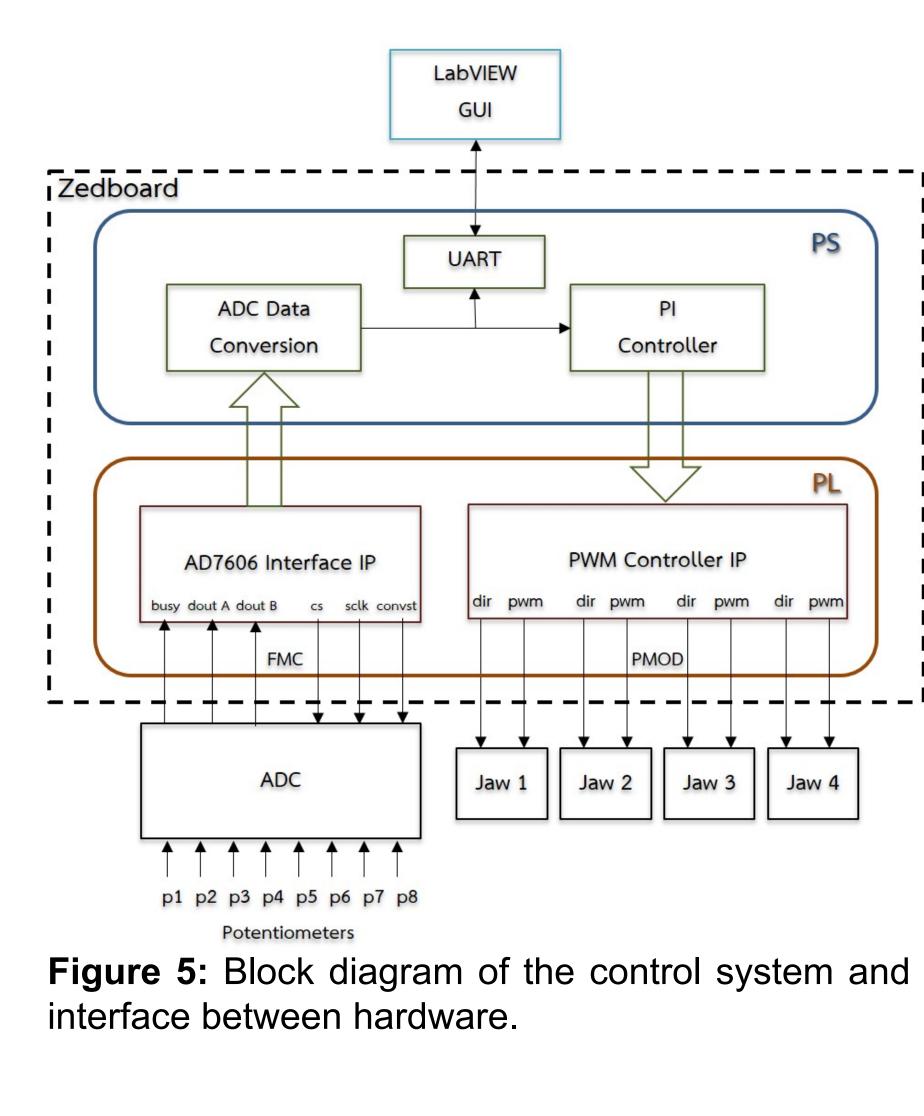

Digilent's Zedboard featuring a Zynq XC7Z020 is chosen. Analog Devices' EVAL-AD7606SDZ and FMC adapter board are selected for a multi-channel bipolar simultaneous sampling 16-bit ADC. Two custom IPs are implemented in Programmable Logic (PL) part of the Zedboard using VHDL,

1) <u>AD7606 Interface IP</u> is designed with FSM to achieve timing requirements.

2) <u>PWM Controller IP</u> receives duty cycle in BCD form via AXI bus to generate PWM signals.

**Figure 2:** (left) In-house PWM drive PCB and (right) Zedboard and 8-channel ADC.

Software is coded in C in the Processing System (PS) part of the Zedboard. Three main parts, PI controller, ADC Data Conversion, and UART, are implemented in the PS. Collimator position can be displayed via LabVIEW GUI and the set points can be set and sent to PS. Both are through UART.

Two custom IPs in the PL send and receive information to PS via AXI bus interface. FMC connector is for ADC interface and PMOD connector is for PWM signals.

| OMMUNICATION<br>VION<br>RS-232 Status<br>SA resource name                                            | SYSTEM<br>ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | STATUS<br>Hardware ON<br>Position SENT     |                                                                                                  |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------|

| COM3  aud rate 115200 ata bits 8 arity None stop bits 1.0 ow control None delay before read (ms) 330 | Desired Position          Set Position         Jaw1       Jaw2         2000       2000         Jaw3       Jaw4         0       0         SET HOME       Image: Comparison of the set of the | Output PositionJaw1Jaw219991999Jaw3Jaw4-25 | Position<br>(Redundant Channels)<br>Jaw1 (R) Jaw2 (R)<br>3048 5847<br>Jaw3 (R) Jaw4 (R)<br>3 -11 |

#### Figure 6: LabVIEW GUI.

http://www.slri.or.th

### **Result and Discussion**

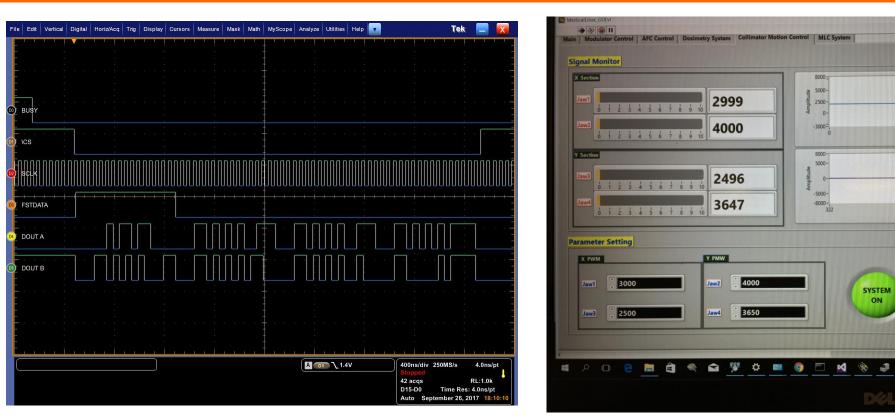

Interface between the ADC board and FPGA was tested. The signals from FPGA to ADC are chip select (cs), serial clock (sclk), and conversion start (convst), and the signals from ADC to FPGA are busy and digital data in serial form (dout A and dout B). The result shows that all signals meet timing requirements and we receive correct information from all eight 16-bit channels with a 20 MHz sclk. The same result is also obtained from using higher sclk frequency up to 30 MHz. The result of the step response, with the best tuned gains of PI controller, was observed. The expected result of the overall system response is obtained and very satisfactory.

**Figure 7: :** (left) Interface signals between FPGA and ADC, and (right) step response of the system.

roengrut@slri.or.th (Corresponding author)

### Nakhon Ratchasima, THAILAND