# It's all about time

### Software and Hardware Timing Elements

Jacob Kornerup, Ph.D.

LabVIEW R&D

National Instruments

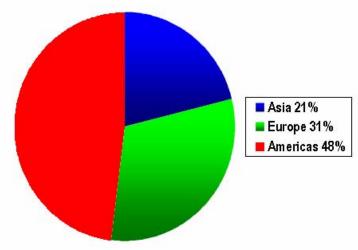

Leaders in Computer-Based Measurement and Automation

- Founded in 1976

- Based in Austin, Texas

- More than 4,000 employees;

operations in 40+ countries

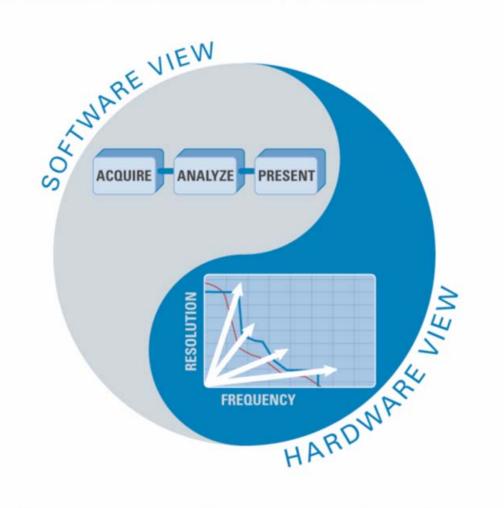

### **National Instruments Vision**

**Graphical System Design**

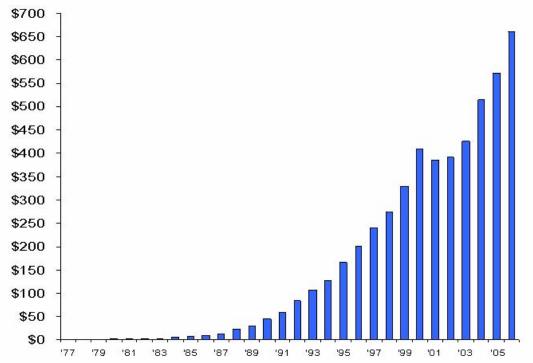

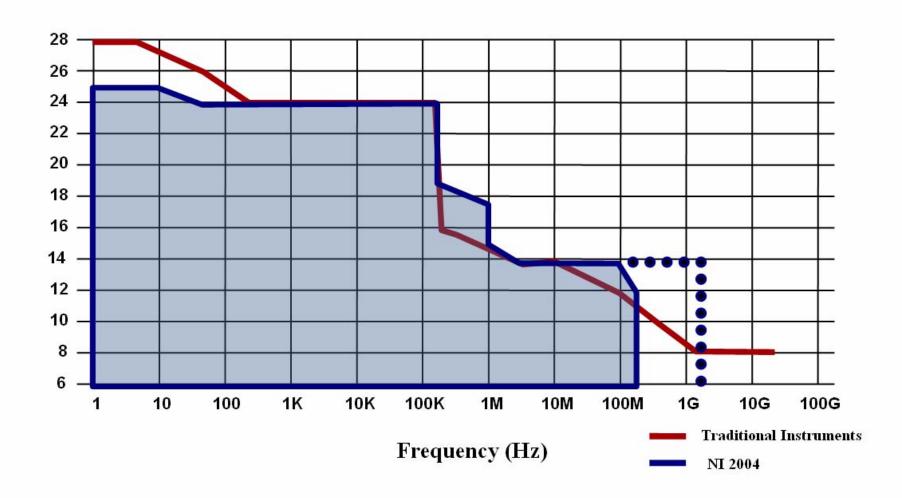

### Leveraging Semiconductor Technology

### Leveraging Semiconductor Technology

# **Agenda**

- Importance of Timing

- Role of Time in Measurements

- Role of Time in Concurrency

- Timing Technology Enablers

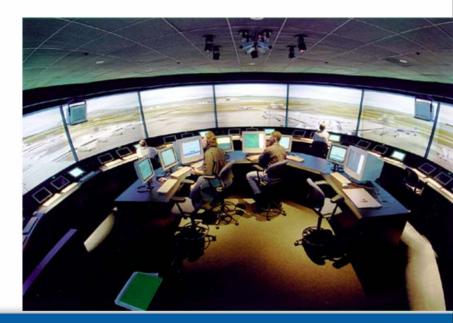

# The world without timing

**Functionality**

Safety

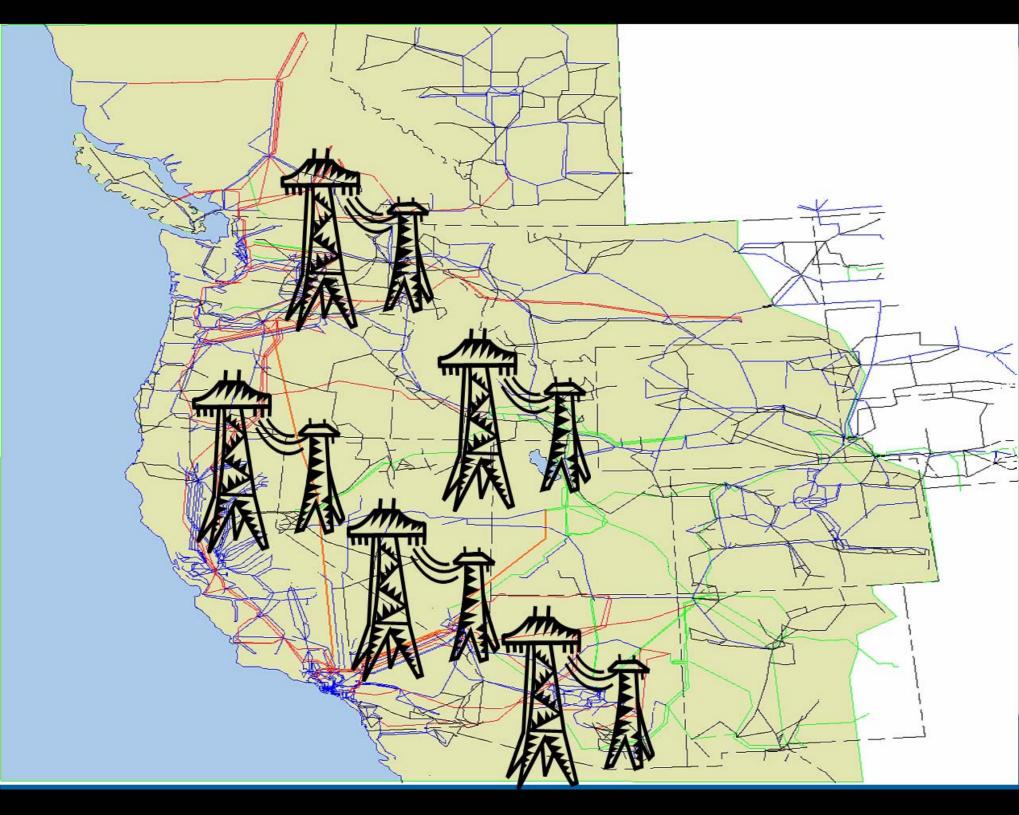

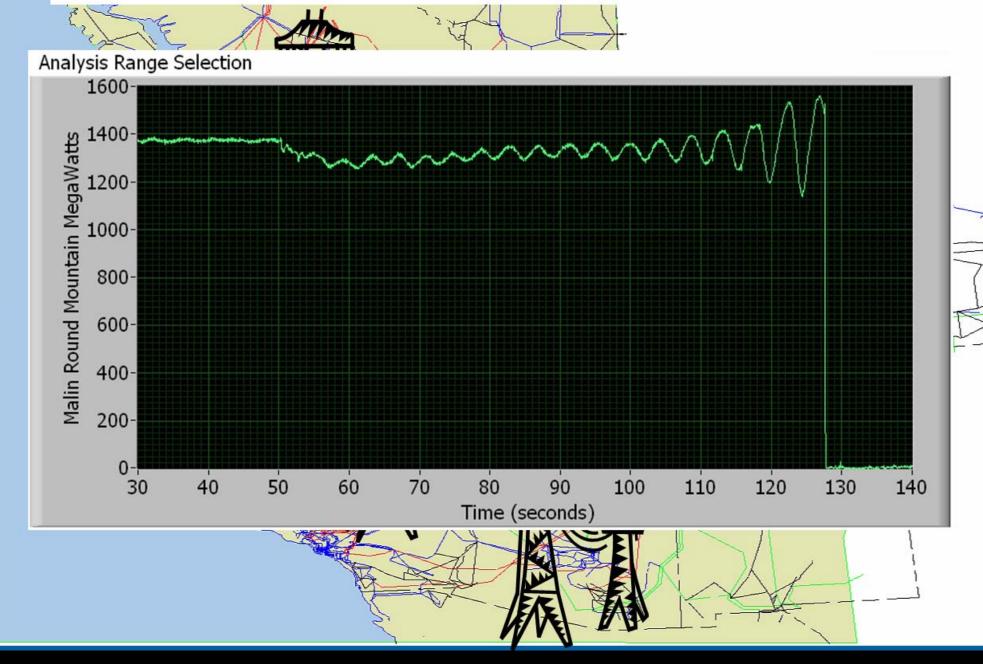

### Actual Data from August 10th, 1996 Blackout

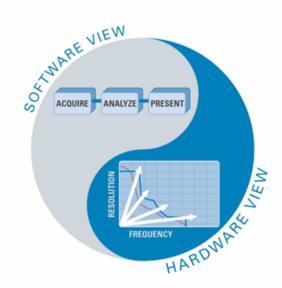

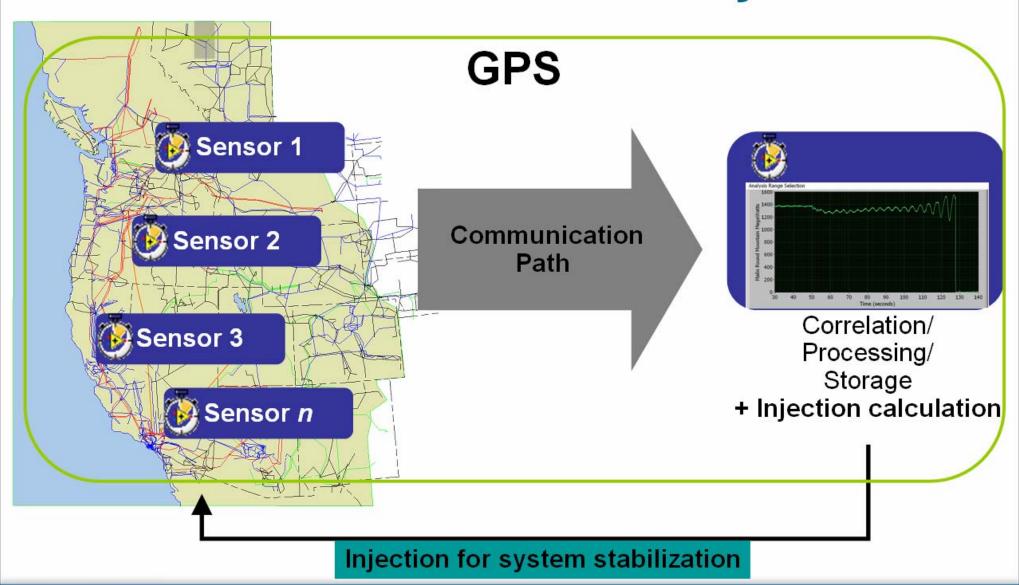

# **GPS Enables Stabilization System**

### The Role of Time in Measurements

### **Timing Considerations for Measurements**

- Sample rates determined by physical phenomenon

- Triggers from external events

- Timed stimulus/response measurements

- Global triggers and clocks for synchronizing multiple measurement devices

- Buffers and FIFOs for storing acquired data

- Interrupts for transferring data

# **Technologies for Time and Concurrency**

Time Scale

Nanoseconds

Microseconds

Milliseconds

Backplane timing

IO synchronized with a global clock

Software programmed FPGAs

**Timed Loops**

Software constructs: FIFOs and Queues

**Structured dataflow**

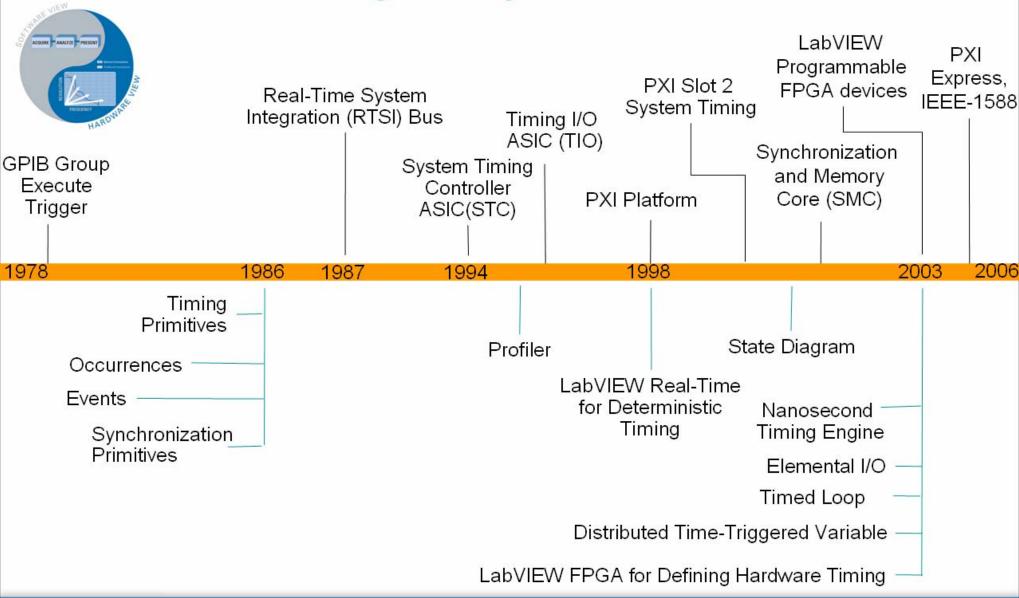

### 30 Years of NI Timing and Synchronization Innovation

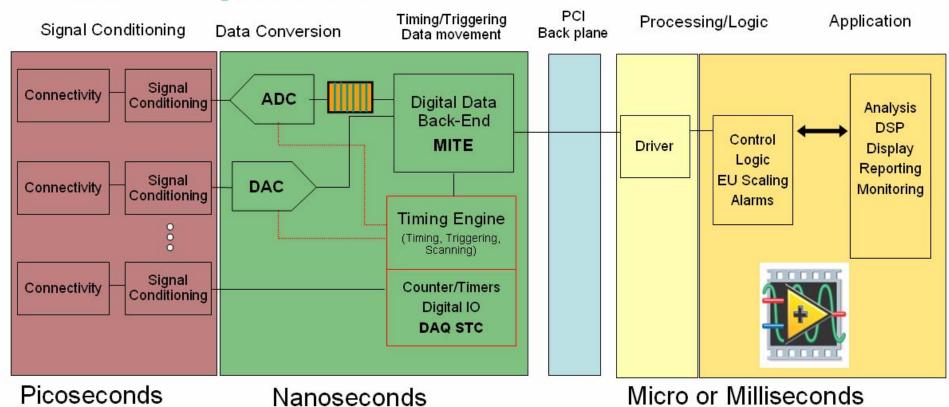

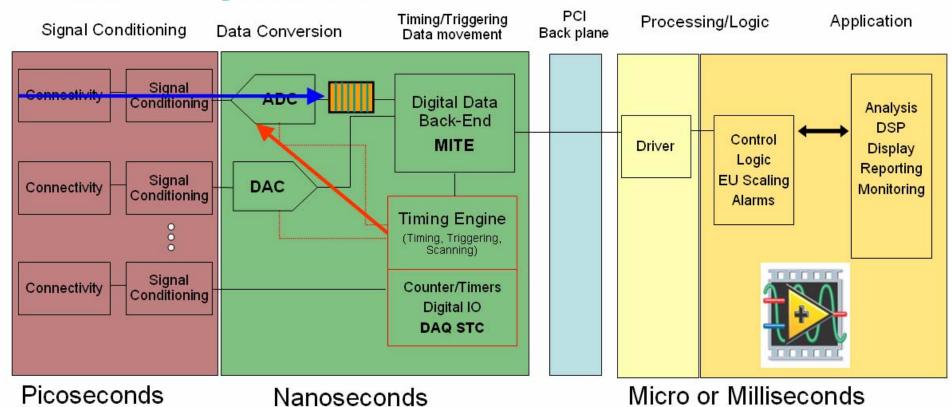

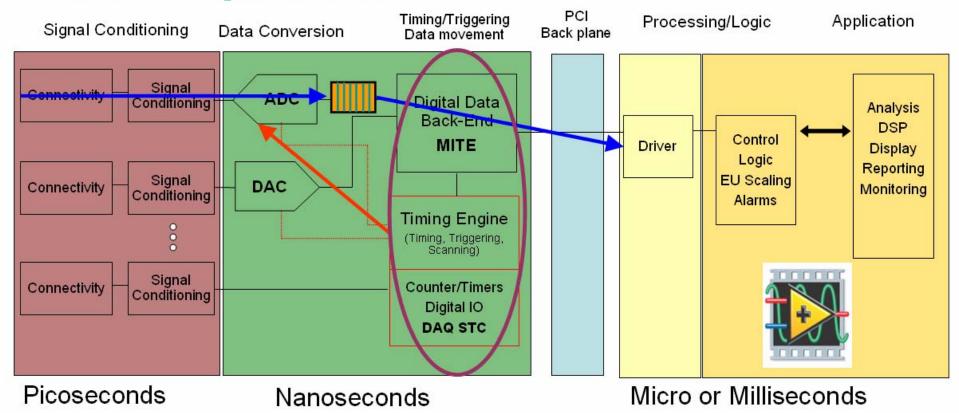

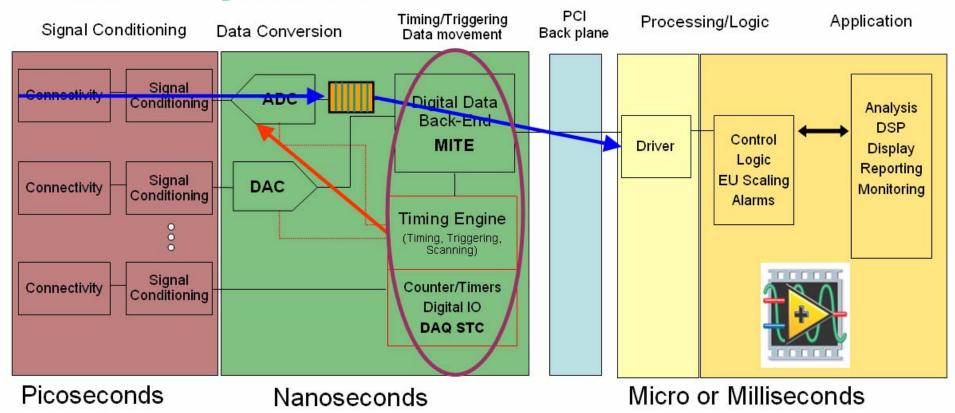

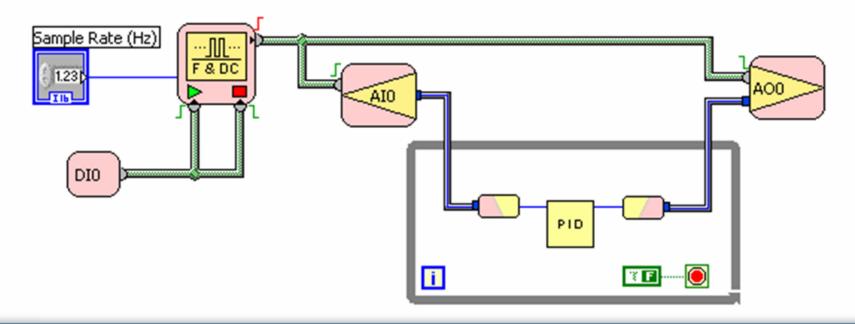

IO "Operating System" implemented in

- IO "Operating System" implemented in hardware

- Continuous or finite, hardware-timed acquisition

- Host application does not need to be real-time

### **Considerations for Distance and Delay**

- The delay of a signal is proportional to its travel distance

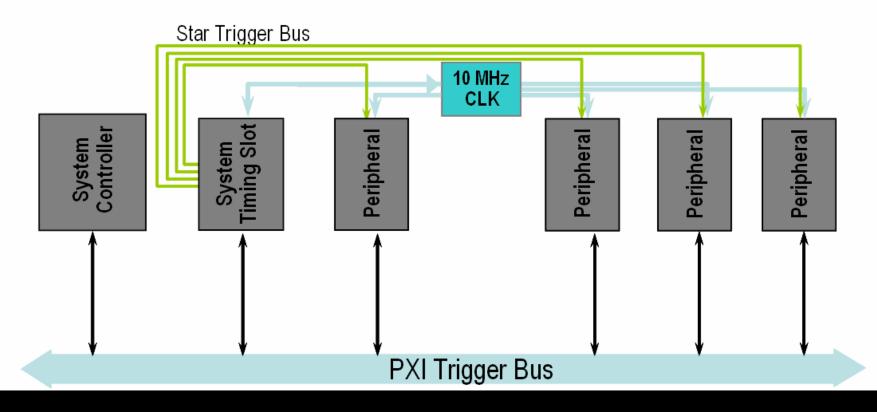

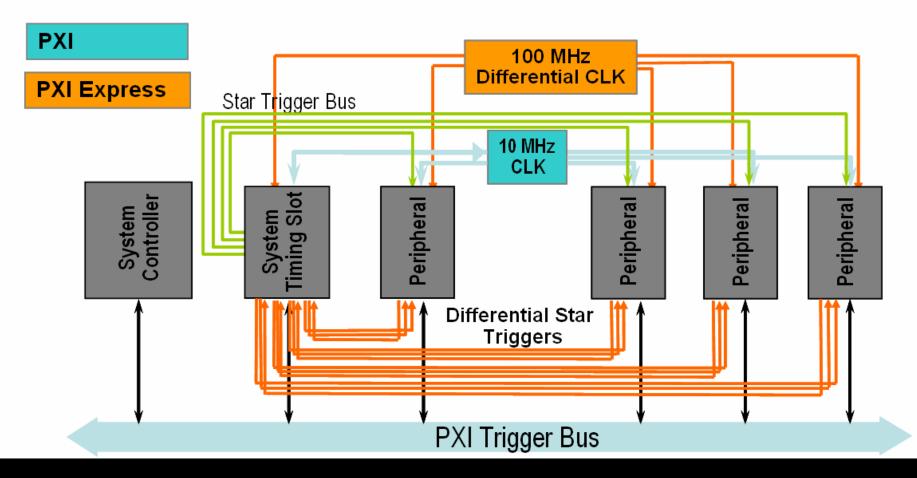

- PXI platform provides Star triggers

- all trigger signals have the same delay (<1 ns PXI, <150ps PXI Express)</li>

PXI

# **Considerations for Distance and Delay**

- The delay of a signal is proportional to its travel distance

- PXI platform provides Star triggers

- all trigger signals have the same delay (<1 ns PXI, <150ps PXI Express)</li>

### **PXI Combines Standard Technologies**

PXI controller

OS Technology

ADEs

Chassis

\*Bus Technology

•Timing

•Synchronization

Peripheral Slots

Over 1500 PXI Products from over 70 Vendors

Systems Alliance

PXI backplane

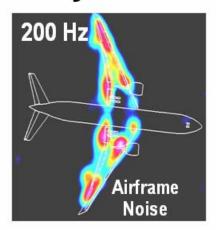

### **Flyover Test**

### Signal-based, synchronous and Distributed System

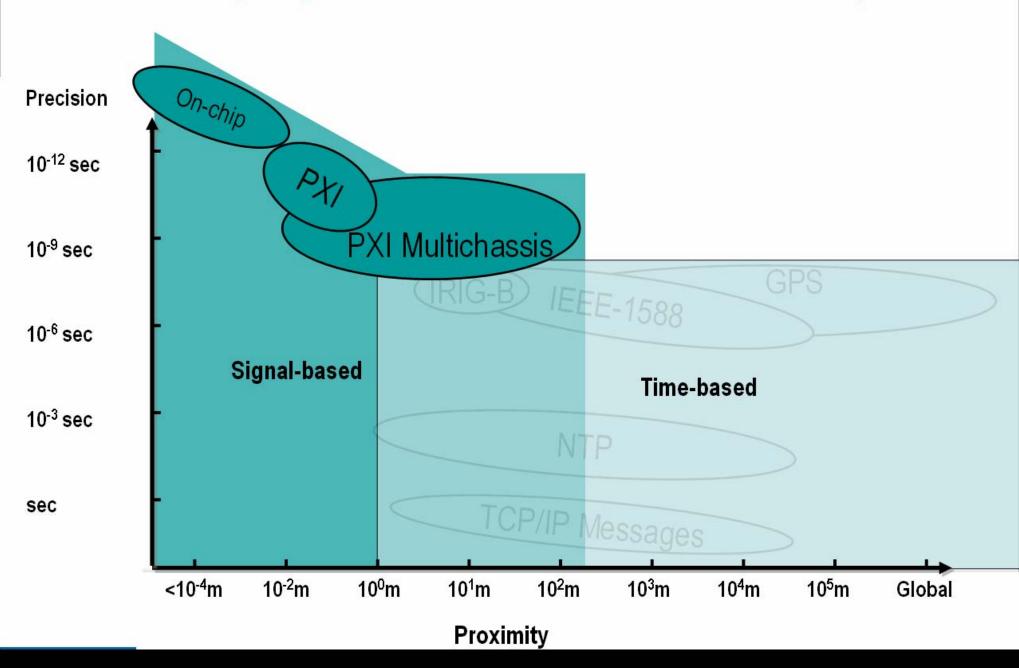

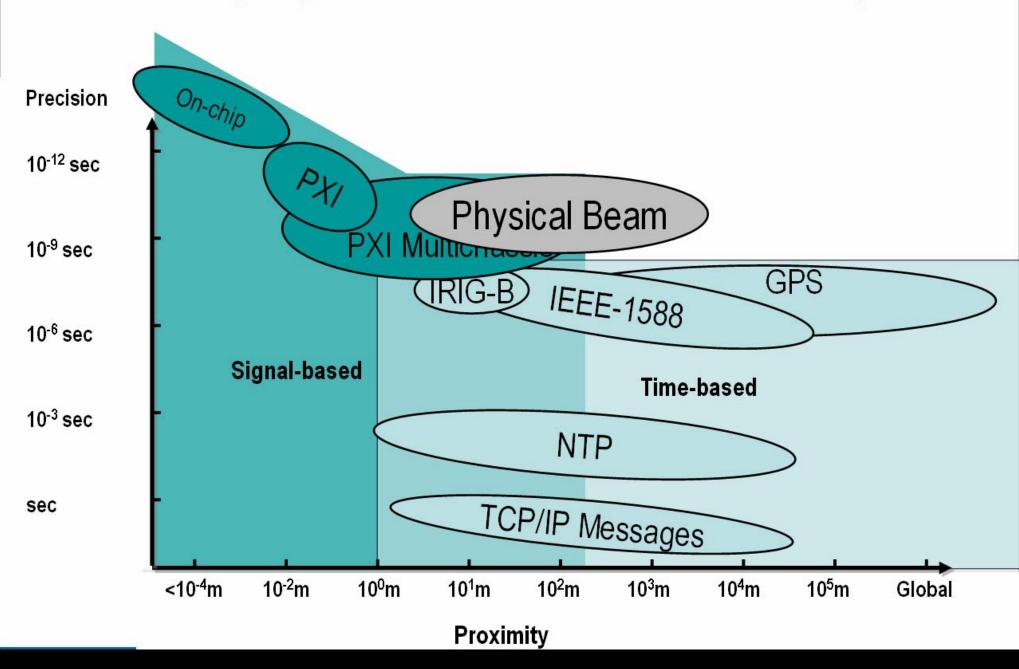

# **Comparing Synchronization Technologies**

# **Comparing Synchronization Technologies**

# **Comparing Synchronization Technologies**

# Picosecond-Level Synchronization

### with NI TClk Technology

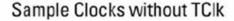

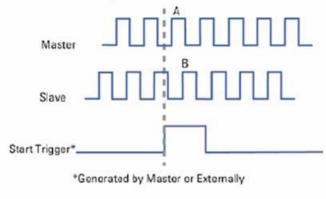

#### Sample Clocks with TClk

### **Trigger Clock (TCIk)**

- Modular Instruments

- Synchronization and Memory Core (SMC)

- Typical skew < 1ns, jitter < 10ps</li>

- Less skew with calibration

- Aligns sample clocks that may not be aligned initially despite being phase locked

### The Role of Time and Concurrency

# The Free Lunch Is Over Multi-core is here

"The concurrency revolution is likely to be more disruptive than the OO revolution..."

Herb Sutter

Microsoft

The Free Lunch Is Over

# **Traditional Development Tool Challenges**

**Priority Inversion**

Deadlock/Livelock

**Thread Synchronization**

**Processor Cache Effects**

Race Conditions

Scalability to Multiple CPUs

**Sequential Performance**

Lock Contention

Flow of Data

Non-Determinism

**Load Balancing**

### **Thesis**

- Embedded software is not just software on small computers.

- Time and concurrency are essential in embedded software.

- Platforms are essential in the design of embedded software.

- Platforms need good modeling properties (model-based design).

- Object-oriented design cannot provide these modeling properties.

- Actor-oriented design offers better concurrency and time.

- Behavioral types offer a truly practical form of verification.

Source: An Overview of the Ptolemy Project and Actor Oriented Design Presentation

### **Traditional Programming Languages**

Ignore both time and I/O and have problems dealing with concurrency

- I/O has been managed by a driver with no presence in the language

- I/O should be an integral part of the language

- Time is not a part the language

- Add time to the language to reduce the complexity for both computation and I/O

- Sequential nature of threads adds complexity to I/O processing

- An actor-oriented approach is inherently concurrent

# **Timing Technology Enablers**

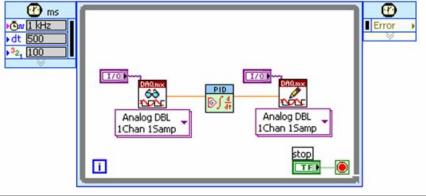

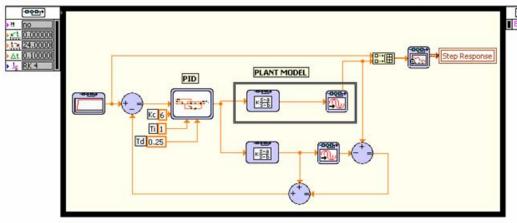

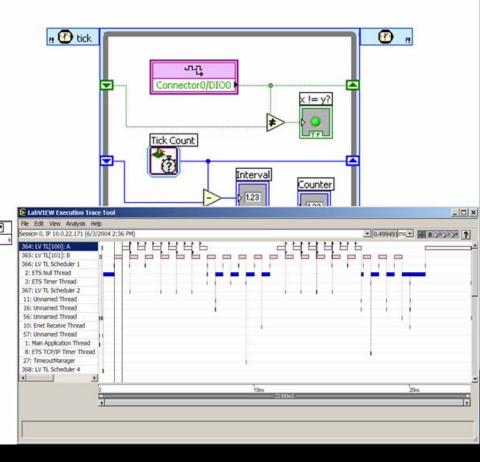

# **Graphical Timing Options**

- Multi-rate time-critical loops

- Microsecond timing

- Single-cycle FPGA timing

- Simulation loop structures

- Real-Time trace tool

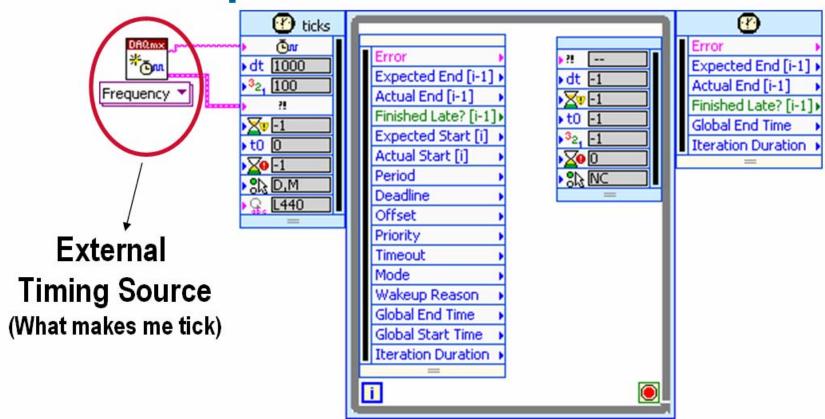

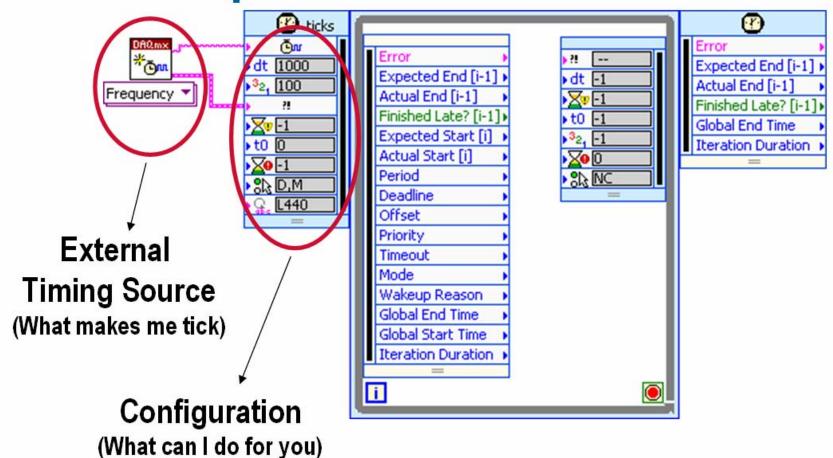

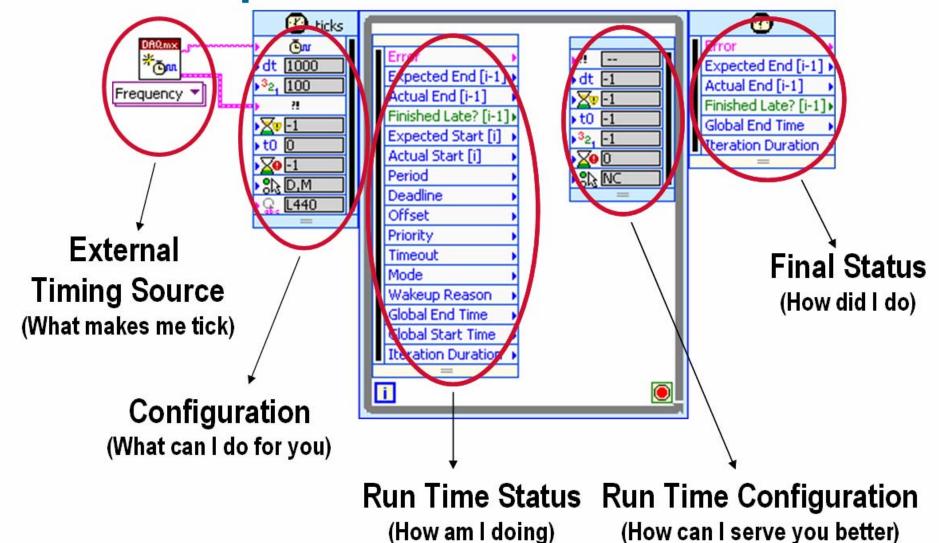

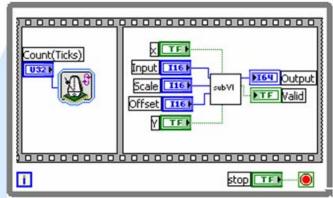

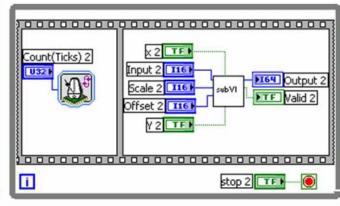

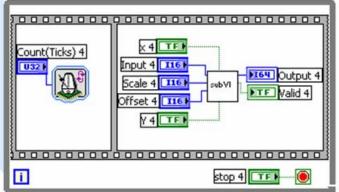

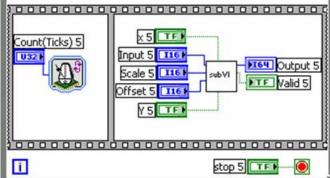

# Timed Loop in LabVIEW

### Timed Loop in LabVIEW

### Timed Loop in LabVIEW

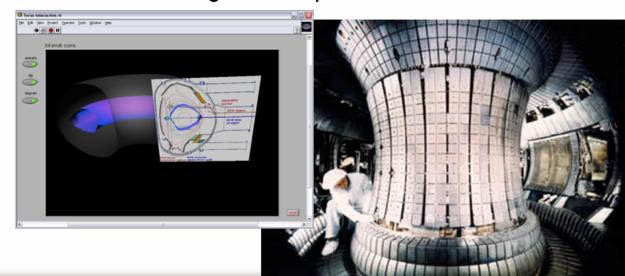

### **Multicore Process Control for Plasma Control**

- Max Planck Institute (Munich, Germany)

- Plasma control in nuclear fusion tokamak with LabVIEW on an 8 core real-time system

"...with LabVIEW, we obtained a **20X processing speed-up** on an octal-core processor machine over a single-core processor..."

Louis Giannone Lead Project Researcher Max Planck Institute

# FPGA Programming: The Ultimate in Multicore, Multiprocessor Development

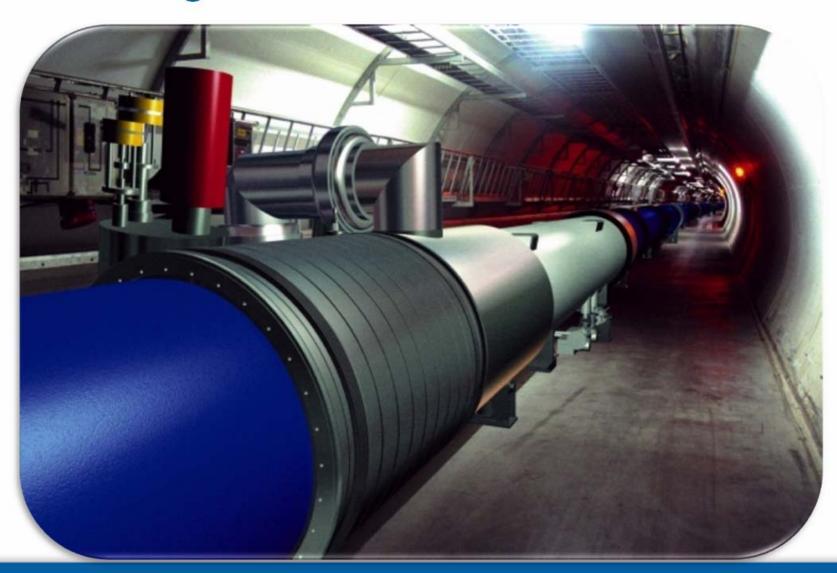

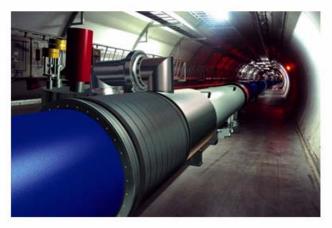

# **CERN Large Hadron Collider**

From IEEE Real Time Conference 2007. Used with permission.

- The LHC collimator: system

- Control requirements

- Control system layout

- •The RT platform used

- Control system software architecture

- The MDC

- The PRS

- Conclusions

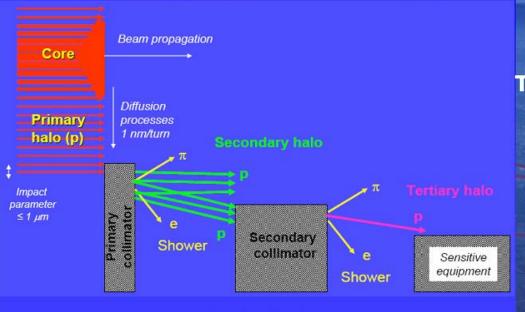

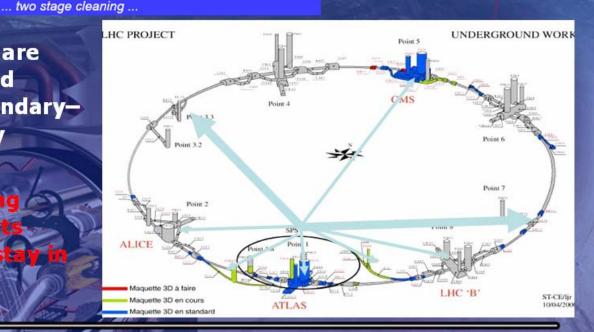

### The LHC collimators system

The collimation system is based on different collimators types and

up to 108 collimators distribuited over 6 points in the machine

Jaw positions are correlated primary — secondary—

tertiary

Also during movements they have to stay in sync

A. Masi, R. Losito, LHC Collimators low level control system

- The LHC collimators system

- Control requirements

- Control system layout

- The RT platform use:

- Control system

software architecture

- The MDC

- The PRS

- Conclusions

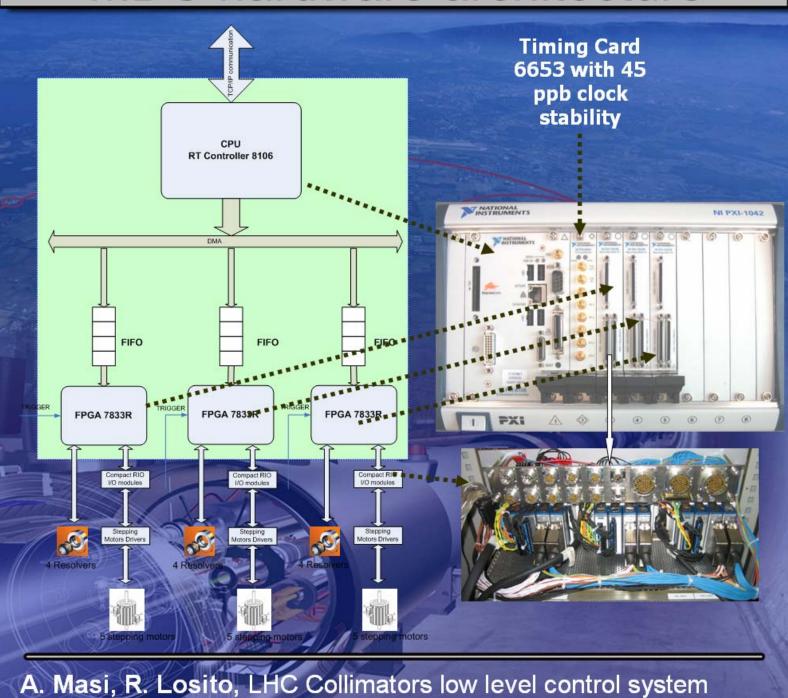

### The RT platform used

PXI systems by National Instruments have been used as RT platform because of:

- their robustness and compactness

- the new RT controllers based on Intel Dual Core processors with solid state disk are powerful and reliable

- the built-in 10 MHz signal architecture allows easy daisy chaining of a synchronization clock across multiple chassis through BNC connectors on the back of the chassis

- 3 Mgate FPGA cards with integrated digital and analog I/O are available

- A wide variety of cards is available and provided with LabView RT drivers. This allows saving manpower on the drivers' development

A. Masi, R. Losito, LHC Collimators low level control system

From IEEE Real Time Conference 2007. Used with permission.

### Road Map

- The LHC collimators system

- Control requirements

- Control system layout

- •The RT platform used

- Control system

software architecture

- The MD(

- The PRS

- Conclusions

### MDC hardware architecture

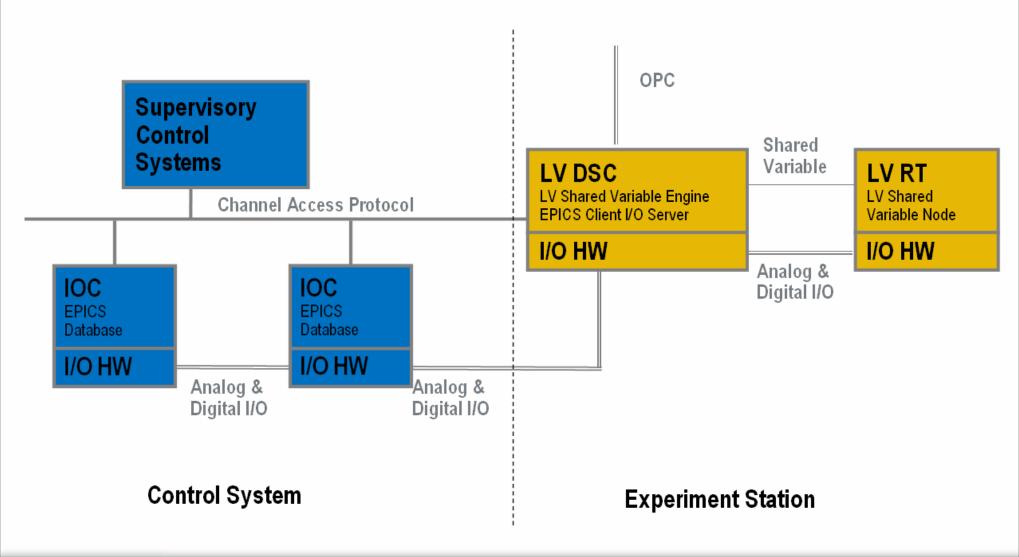

### **EPICS and LabVIEW**

### **High-Level Design Models**

# The Future of Timing and Synchronization

- Focus on the particulars you care about

- Hide the details you don't care about

- Introduce a "Timing Wire"

- Since time is an integral part of the system

### Graphical System Design It's all about time

LEGO MINDSTORMS NXT "the smartest, coolest toy of the year"

CERN Large Hadron Collider "the most powerful instrument on earth"