# HIGH-SPEED DIRECT SAMPLING FMC FOR BEAM DIAGNOSTIC AND ACCELERATOR PROTECTION APPLICATIONS

Johannes Zink

7<sup>th</sup> IBIC, Shanghai 2018

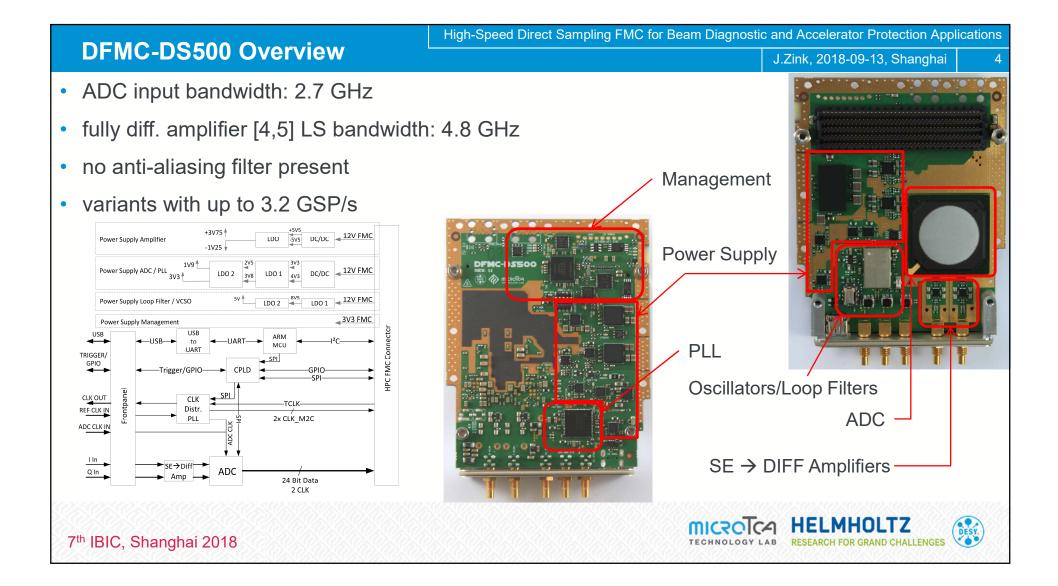

### **DFMC-DS500** Overview

#### High-Speed Direct Sampling FMC for Beam Diagnostic and Accelerator Protection Applications

#### J.Zink, 2018-09-13, Shanghai

- single width FMC according to ANSI/VITA 57.1 standard

- 8.5 mm stacking height

- air cooled, shielding cage + heatsink planned

- front panel: 5 RF SSMC + 1 HDMI Type D (micro) connectors

- 12-Bit, 500/800 MSP/s Dual Ch., 1/1.6 GSP/s Single Ch.

TECHNOLOGY LAB

HELMHOLTZ

GRAND CHALLENGES

DESY.

7<sup>th</sup> IBIC, Shanghai 2018

|                                                                                                                                                                                               | High-Speed Direct                                                                              | High-Speed Direct Sampling FMC for Beam Diagnostic and Accelerator Protection Applications                                                                                                                                           |                |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| DAQ-FPGA                                                                                                                                                                                      |                                                                                                | J.Zink, 2018-09-13, Shanghai                                                                                                                                                                                                         | 5              |  |

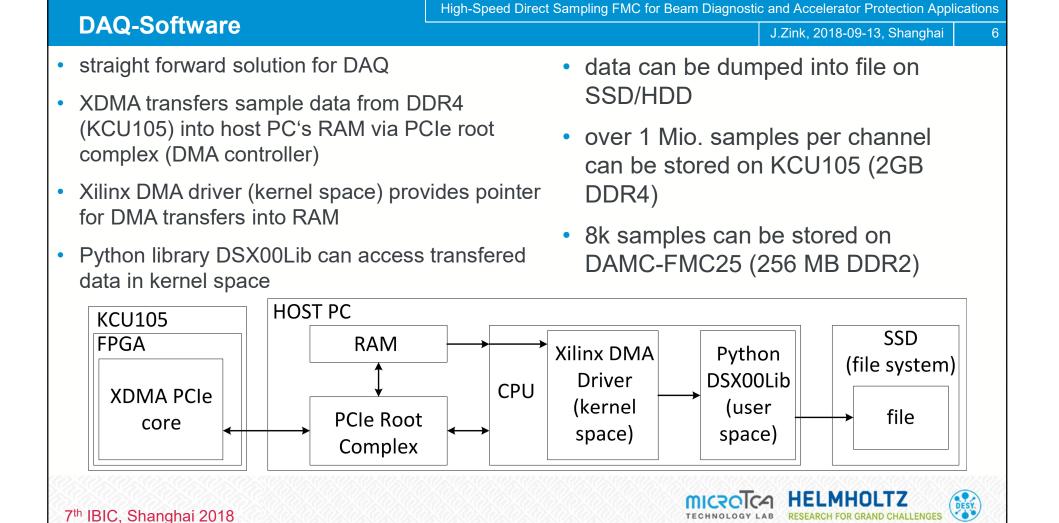

| <ul> <li>DFMC-DSX00-INTERFACE connected data lanes → delay calibration</li> </ul>                                                                                                             | ected to LVDS                                                                                  | <ul> <li>AXI_DMA dumps data into DDR4 via<br/>AXI SmartConnect</li> </ul>                                                                                                                                                            |                |  |

| <ul> <li>DSX_PKT_GEN generates AXI str<br/>readable by AXI DMA core</li> </ul>                                                                                                                | eam pakets                                                                                     | <ul> <li>XDMA PCIe core controls cores via AXI<br/>Lite</li> </ul>                                                                                                                                                                   |                |  |

| (see also THOA01, IBIC 2018, J.Marjanovic for d                                                                                                                                               | ata post-processing)                                                                           | via SMC $\rightarrow$ reads data from DDR4                                                                                                                                                                                           | pci express x8 |  |

| default_sysck_300                                                                                                                                                                             | dfmc_dsx00_spi_ip_0<br>                                                                        | axi_mem_intercon<br>axi_bram_ctrl_0<br>axi_bram_ctrl_0<br>axi_bram_ctrl_0_bram<br>axi_bram_ctrl_0_bram<br>axi_bram_ctrl_0_bram<br>AXI BRAM_PORTA +<br>AXI BRAM_Controller<br>AXI BRAM_Controller<br>Block Memory Generator<br>ddr4_0 | DSx00_SPI_0    |  |

| FMC_0     fmc_dsx00_interface_0     dsx_pkt_gen_0       FMC_0     fmc_dsx00_interface     fmc_dsx00_interface       fmc_dsx00_interface     fmc_dsx00_interface       7th IBIC, Shanghai 2018 | axi_dma_0<br>+ S_AXI_LITE M_AXI_SG +<br>+ S_AXIS_S2MM M_AXI_S2MM +<br>AXI Direct Memory Access |                                                                                                                                                                                                                                      |                |  |

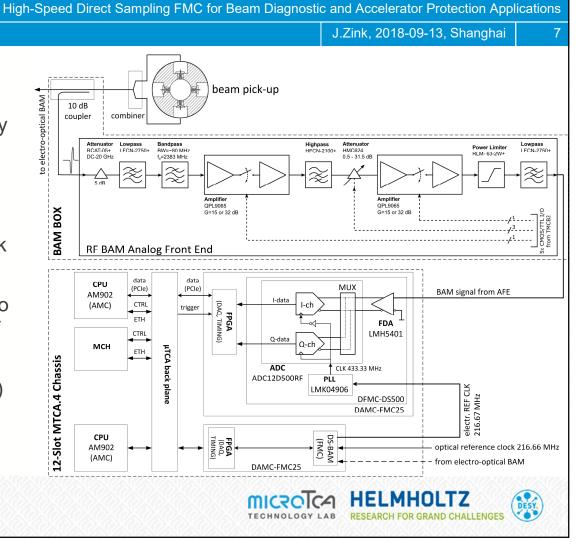

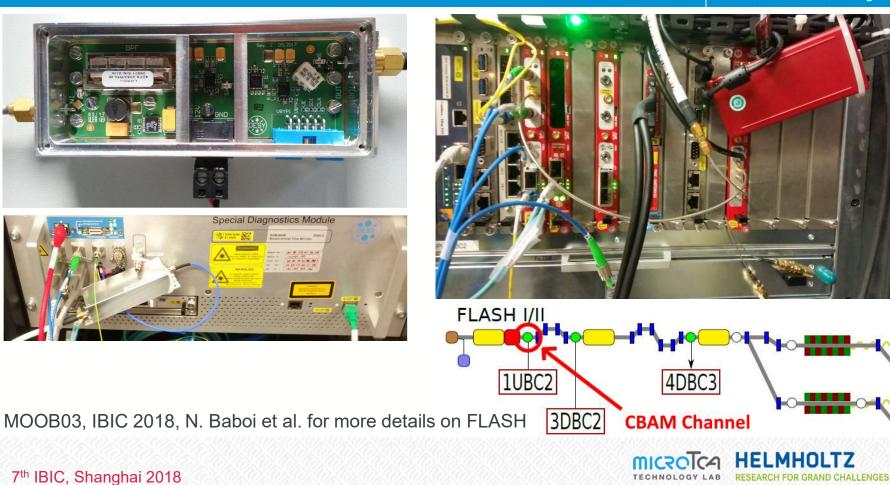

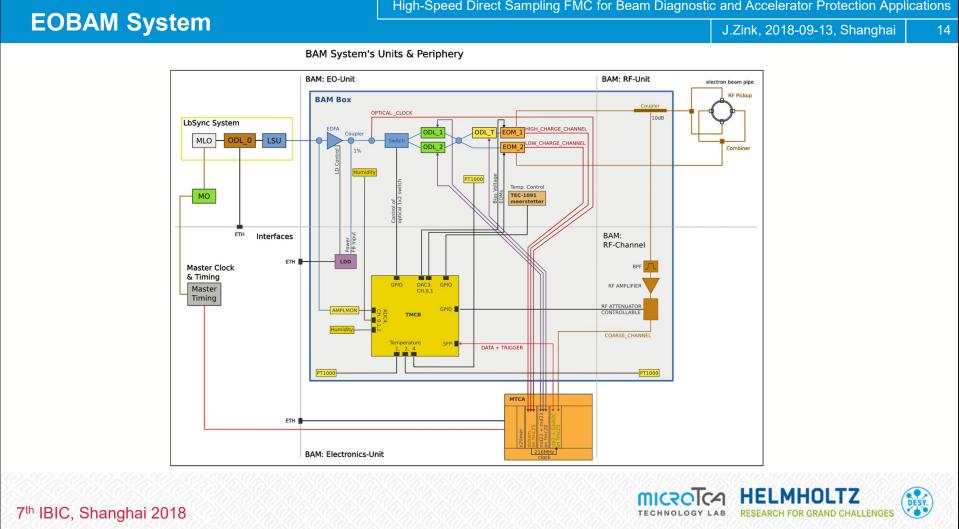

### Coarse BAM Channel

- coarse BAM Channel planned in FLASH

- coarse BAM channel in addition to electro-optical BAM [1,2] → automatically adjust optical delay lines

- uses same combined high-bandwidth pick up [3] signals (40 GHz)

- analog front end bandpass filters the pick up signal

- bunch charges can vary from 20 pC up to 1 nC, which requires a dynamic range of about 34 dB

- sampling (DFMC-DS500/DAMC-FMC25) and processing in MTCA.4 crate

7<sup>th</sup> IBIC, Shanghai 2018

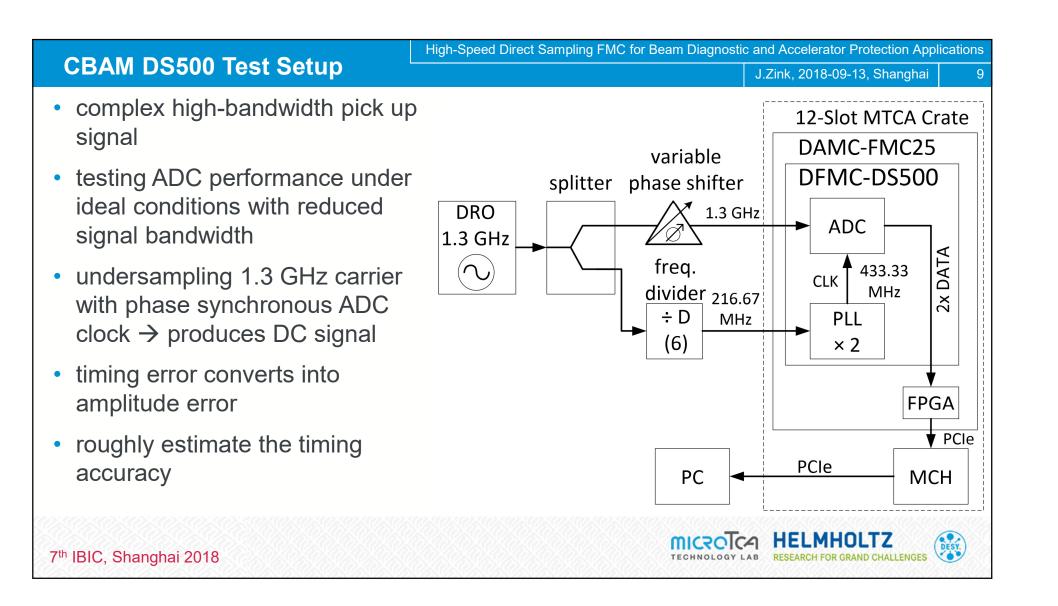

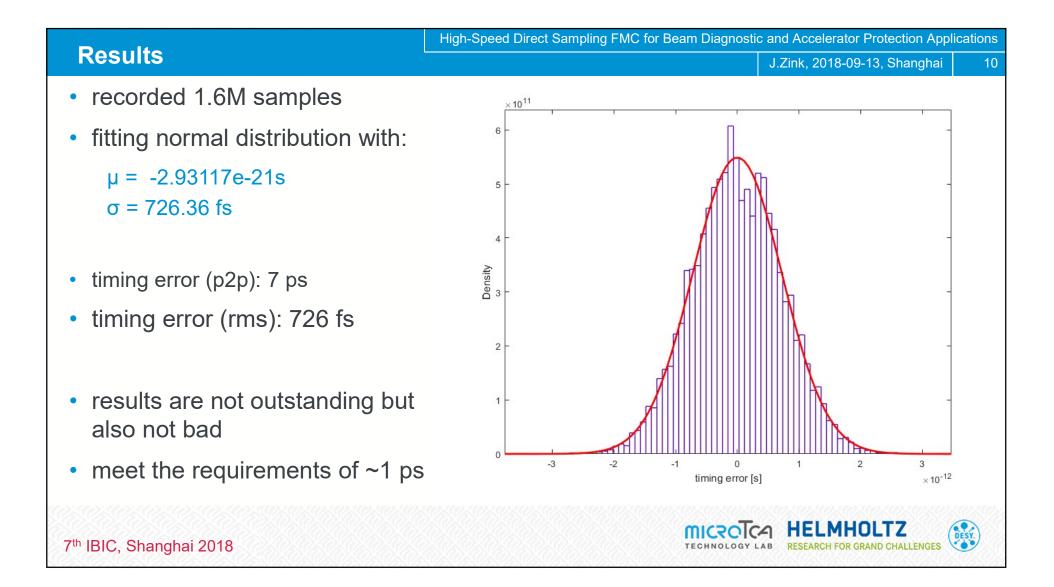

## CBAM Channel in FLASH

High-Speed Direct Sampling FMC for Beam Diagnostic and Accelerator Protection Applications

J.Zink, 2018-09-13, Shanghai

8

DESY.

| High-Speed Direct | Sampling FMC f | or Beam Diagnostic and Acc | celerator Protection Applications |

|-------------------|----------------|----------------------------|-----------------------------------|

|                   |                |                            |                                   |

### References

J.Zink, 2018-09-13, Shanghai

13

[1] Prototype of the Improved Electro-Optical Unit for the Bunch Arrival Time Monitors at FLASH and European XFEL, H. Dinter et al., Proceedings of FEL, 2015

[2] The Bunch Arrival Time Monitor at FLASH and European XFEL, M. Viti et al., Proceedings of ICALEPCS, 2017

[3] High bandwidth pickup design for bunch arrival-time monitors for free-electron laser, A. Angelovski et al., PHYSICAL REVIEW SPECIAL TOPICS - ACCELERATORS AND BEAMS, 2012

[4] Driving the GSPS ADCs in Single-Channel or Dual-Channel Mode for High Bandwidth Applications, M. Plisch, J. Brinkhurst, TIDU175 Texas Instruments Incorporated, July 2012

[5] Stabilizing Differential Amplifiers as Attenuators, L. Siebert, TIDA00522 Reference Guide, Texas Instruments Incorporated, August 2016

High-Speed Direct Sampling FMC for Beam Diagnostic and Accelerator Protection Applications