# TRANSVERSE BUNCH-BY-BUNCH FEEDBACK SYSTEM FOR THE SPRING-8 STORAGE RING

T. Nakamura<sup>#</sup>, S. Daté, K. Kobayashi, T. Ohshima, JASRI/SPring-8, Hyogo, Japan

#### Abstract

Transverse bunch-by-bunch feedback system for the SPring-8 storage ring is in operation from January 2004 and suppresses both the horizontal and vertical instabilities without any troubles and any additional tuning during these half years. To reduce the residual motion caused by noises in position signal, the system achieved high signal-to-noise ratio with high-resolution beam position monitor and 12-bit ADC with analog demultiplexer. Also FPGA is employed for signal processing for simplicity and reduction of cost. The estimation method of the residual motion and the scheme of making FIR filters are also developed.

#### INTRODUCTION

The SPring-8 electron storage ring is the light source and its parameters are shown in Table 1.

Table 1. Parameters of the SPring-8 Storage Ring

| Energy                    | Е                               | 8 GeV        |

|---------------------------|---------------------------------|--------------|

| Average Current           | I                               | 100 mA       |

| Emittance / Coupling      | ε/κ                             | 6 nm / 0.1 % |

| Beta function at feedback | $\beta_{H}$ / $\beta_{V}$       | 25 m / 4 m   |

| Beam size at feedback     | $\sigma_{\rm H}/\sigma_{\rm V}$ | 390μm/ 5μm   |

| Fractional Tune           | $\Delta v_H / \Delta v_V$       | 0.15 / 0.35  |

| Betatron Damping Time     | $\tau_{eta}$                    | 8.1 ms       |

| RF Frequency              | f <sub>RF</sub>                 | 508.58MHz    |

| Revolution Period         | $T_0$                           | 4.8 μs       |

Before the feedback, the high chromaticity was used to suppress transverse instabilities, driven by resistive wall of in-vacuum insertion devices and higher order modes of cavities [1]. However the further increase of the chromaticity is limited by power supplies and by reduction of the dynamic apertures. The increase of the beam current and the reduction of the emittance by lowering the energy are recently planed to obtain more brilliance and both increase the strength of instabilities. And also even under the current chromaticity, the loss of injected beam at low gap sections is large and this should be avoided at the "top-up" injection [2,3]. "Top-up" also requests the fast damping of motion excited by slightly unclosed injection bump and its error [4].

The feedback is installed to fulfil these requirements.

One of the problems of feedback systems is the residual motion caused by feedback itself excited by noises in position monitor signal. The SPring-8 feedback is designed to reduce the residual motion to acceptable level compared with the vertical beam size or the diffraction

limit photon size for hard x-rays (less than 1µm) by high-resolution beam position monitors (BPM) and 12-bit resolution ADCs. FPGA is employed for signal processor and only a few FPGA chips are required for our feedback and this simplify the system and reduces the cost.

# **BLOCK DIAGRAM**

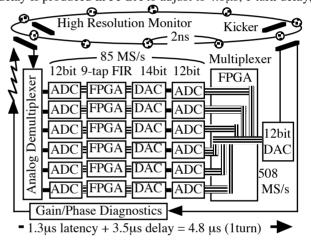

The block diagram of the feedback is shown in Figure 1. The latency of the system from the monitor to kicker is 1.3µs (including 0.3µs in cables) and additional 3.5µs delay is produced in FPGA to adjust to 4.8µs, 1 turn delay,

Figure 1. Block diagram of the feedback system.

## RESIDUAL MOTION

The amount of the residual motion of the beam caused by the noises  $\delta$  in the position signal, is obtained as

$$\sigma_x = \left(\sqrt{T_0 \tau} / \tau_{FB}\right) G(v) \sigma_\delta \tag{1}$$

where  $\tau$  and  $\tau_{FB}$  are total damping time and feedback damping time, respectively, and G(v) is the gain of an FIR filter and is ~1 around reference tune of the filter. For the SPring-8 ring, it is  $\sigma_x = 0.1\sigma_\delta$  with  $\tau \sim \tau_{FB} = 0.5$ ms.

# **DEMULTIPLEXER AND 12-BIT ADC**

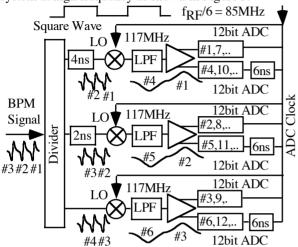

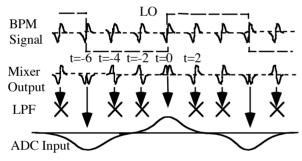

The feedback employs 12-bit ADC of 85MS/s to be free from the tradeoff of dynamic range and resolution, and from the offset correction. Those are required with 8-bit ADC of 508MS/s. The 6-way analog demultiplexer is developed for 12-bit ADCs that require low frequency signal in our case and is effective for slower devices. The diagram and the principle of the demultiplexer are shown in Figure 2 and Figure 3, respectively. The BPM signal is a bipolar pulse train and is mixed with a square wave signal (LO) of frequency 85MHz, one sixth of RF frequency. The bipolar pulses mixed at the timing of zero crossing of LO is converted to unipolar pulses which have

<sup>#</sup>nakamura@spring8.or.jp

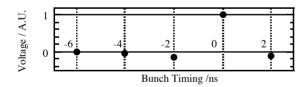

low frequency component and pulses at other timing are stay bipolar. At a low pass filter, the bipolar pulses are blocked, while unipolar pulses can pass to ADC input. Actually, the bipolar pulses penetrate the filter with some amount and get mixed with unipolar pulse component. The contribution of signals of neighboring bunches to unipolar pulse at t=0 measured by a test bench are shown in Figure 4. However, this improves the gain of the system at high frequency as shown in Figure 5.

Figure 2: Analog Demultiplexer.

Figure 3: Principle of analog demultiplexing

Figure 4: Contribution from neighboring bunches at ADC input sampled at t=0. Horizontal scale is the timing of bunches as shown in Figure 3, and vertical is the voltage normalized to the signal at t=0.

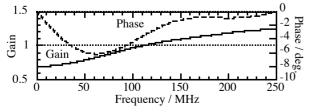

Figure 5: Frequency response produced by the data in Figure 4 by treating them as an FIR filter coefficients.

#### FIR FILTER

To obtain coefficients of FIR filter, the least square fitting method is used. The fitting function is expanded as

$$y[n] = A \sin((1+\Delta)\phi_n + \psi) + B$$

$\cong P_0 \cos \phi_n - P_1\phi_n \sin \phi_n + Q_0 \sin \phi_n + Q_1\phi_n \cos \phi_n + B$  (2) where A,  $\Delta$ ,  $\psi$  and B are amplitude, shift of tune, phase and offset, respectively, and  $\phi_n$  is the reference value of the betatron phase at n-th turn and phase of current turn is set to  $\phi_0 = 0$ .  $P_0 = A \sin \psi$ ,  $Q_0 = A \cos \psi$ ,  $P_1 = P_0 \Delta$  and  $Q_1 = Q_0 \Delta$  are treated as unknown coefficients and position data of M previous turns, y(i), i = 1, 2, ..., M, are used for fitting to make M-tap FIR filter. Then the coefficients  $P_{0,1}$  and  $P_{0,1}$  are obtained as a linear function of  $P_0$  and required signal for feedback kickers is obtained as a form of

$$A\sin(\theta + \psi) = P_0 \cos \theta + Q_0 \sin \theta = \sum_{k=1}^{M} a_k y(k)$$

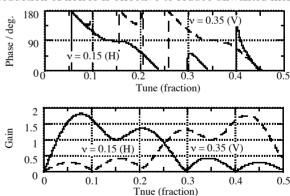

where  $\theta$  is required angle and  $a_i$  are FIR filter coefficients that are the function of  $\phi_n$ .  $P_{0,1}$  and  $Q_{0,1}$  are actually not independent however "ideal" y(i) are data of a sinusoidal motion and this automatically fulfils the relation between  $P_{0,1}$  and  $Q_{0,1}$  and resulting FIR filter should have good response near the reference tune value. This method can extend to 2nd or more order expansion of Eq. 2 with more taps. The 9-tap FIR filter with successive 9-turns data is used and its frequency response is shown in Figure 6. For storage rings, 5-tap is enough however the 9-tap filter has gain only at the neighborhood of tune, which reduces the noises at monitoring, and has no ambiguity to choose the data points for FIR tap. At the application to several-path system such as ERL, this reduction of noises is effective to reduce unwanted kick.

Figure 6: 9-tap FIR filter Response. Fractional tune of horizontal and vertical are 0.15 and 0.35, respectively.

# DIGITAL SIGNAL PROCESSING

The demultiplexed six analog signals are fed to six commercial modules, HUNT Engineering HERON IO-2V, that has two 105MS/s 12-bit ADCs (AD9432), one FPGA (Xilinx XC2V1000) and two 125MS/s 14-bit DACs (AD9767) and is clocked by 85MHz. This FPGA can process two streams of 9-tap FIR filters in parallel hence three boards are enough, however six boards are used and

extra DACs are used for tuning and diagnostics of the system. To multiplex six DAC outputs, special analog multiplexer with six same 12-bit ADCs, an FPGA (Xilinx XC2V250) driven by 254MHz and a 12-bit 508MS/s DAC (Rockwell RDA012) driven by DDR, is developed.

## POSITION MONITOR AND KICKERS

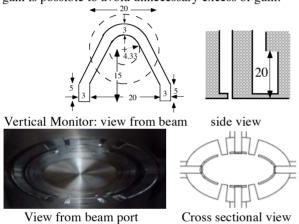

Shorted strip-line type beam position monitor is developed to obtain high output signal. Its shape and picture are shown in Figure 7 and large coaxial feed-thorough are used not to store EM field. The vertical monitor produces more than ten times higher signal than button type monitors and the vertical position resolution ~5µm is obtained for 0.24nC/bunch of multi-bunch mode. From Eq. 1, the expected residual motion is 0.5µm and no degradation of the vertical beam size is observed. The feedback drives two types of striplnie kickers. One is 7cm long and the other is 45cm. The transit time factor at 250MHz is 0.98 and 0.28, respectively, and with them, the adjustment of the frequency dependence of feedback gain is possible to avoid unnecessary excess of gain.

Figure 7: Beam position monitor and kickers. The lower picture is view from beam port and striplines at near side are for 7cm kickers and those at far side are for monitor.

#### DIAGNOSTICS AND INTERLOCK

The gain and phase of the system are continuously monitored. The test signal is up-converted and introduced to the BPM, then processed by the feedback and emerged to kickers output ant it is compared with original one. The frequency of the test signal is 251MHz that corresponds to fractional tune 0.25 where the FIR filter has some gain as shown in Figure 6 and this is far from both tunes (0.15,0.35) hence no beam response is observed. Also the detection circuit of fast beam motion using RF signal from BPM is used for instability interlock to avoid damage of the beam pipe.

## **BEAM TEST**

Damping time of forced oscillation of the beam was measured with small average current but the same bunch current as multi-bunch mode, 20mA/400 bunches. The result is shown in Table 2 and one of the obtained data is

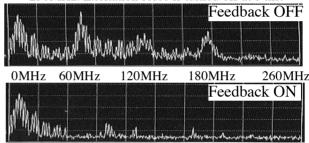

shown in Figure 8. The suppression of horizontal coupled-bunch instabilities driven by higher order modes of acceleration cavities is shown in Figure 9. The single bunch current is limited to 3.5mA/bunch without feedback by mode-coupling instability and the feedback raise the threshold current up to 8mA/bunch.

Table 2: Measured feedback damping time

| Direction \ Frequency | 30kHz(H)/70kHz(V) | ~250MHz |

|-----------------------|-------------------|---------|

| Horizontal            | 0.3 ms            | 1.4 ms  |

| Vertical              | 0.7 ms            | 1.9 ms  |

Figure 8: Damping of vertical forced oscillation of 250MHz. Excitation force is turned off at 0 ms.

Figure 9: Spectrum of horizontal beam signal from 500MHz to 770MHz. Shown frequencies are in baseband. Top: feedback OFF. Many peaks of instabilities are observed. Bottom: feedback ON. Instabilities are suppressed. Residual peaks are harmonics of revolution by non-uniformity of the filling.

## CONCLUSION

The low noise high-resolution transverse bunch-by-bunch feedback system is in operation from January 2004 without trouble, and no additional tuning is required during these half years. And degradation of beam qualities is not observed. For upgrade of the system, merging of digital signal processing stages to a single board is under development for easy maintenance and tuning. Also application to multi-bunch and single-bunch hybrid mode operation is under testing.

# **ACKNOWLEGEMENTS**

M. Shoji and S. Sasaki helped at designing, making and installation of the monitor and kickers. H. Ohkuma and N. Kumagai were giving us continuous encouragement.

## **REFERENCES**

- [1] Related papers are listed in http://acc-web.spring8.or.jp/~nakamura

- [2] M. Takao, et. al., these proceedings.

- [3] H. Tanaka, et. al., these proceedings.

- [4] T. Ohshima, et. al., these proceedings.