TestBed -- Automated Hardware-in-the-Loop Test Framework

# COSYLAB

pavel.maslov@cosylab.com

## Intro

- ☐ Control system updates (>3 times/year)

- DAQ hardware tests:

- manual (+ precise; slow, infrequent)

- automatic (+ fast, repetitive, liberating human resources)

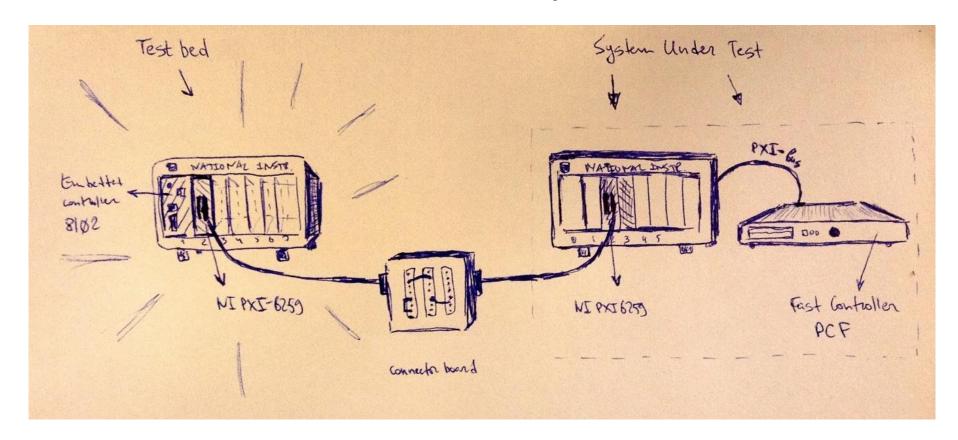

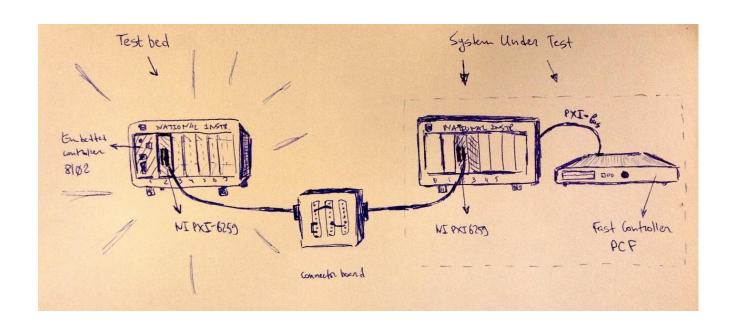

#### **HW** architecture

☐ TestBed chassis is attached to System Under Test

□ TestBed is running SL 6.3 and CODAC 4.1

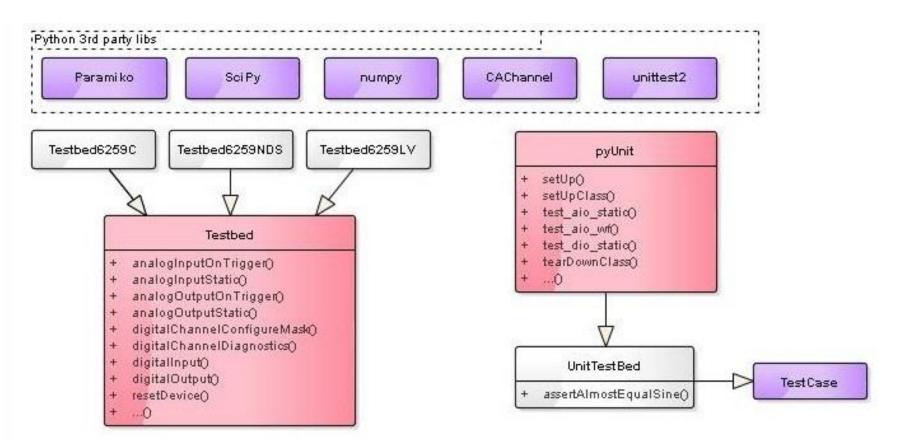

## **SW** architecture

- ☐ The software part consists of 3 tiers:

- Software that provides the desired functionality of a DAQ board:

- C executables

- EPICS device support (NDS driver + IOC)

- LabVIEW interface

- Python bindings in the form of a class

- Automatic test cases written by the test-plan engineer

## **DAQ** functionality

- ☐ The NI-PXI6259 functionality supported in TestBed:

- Device reset

- Digital input/output (static) on a desired line

- DIO diagnostics: port mask and lines state

- Configuration of the DIO port mask

- Analog input/output (static) on a desired channel

- Analog input (waveform) on a trigger

- Analog output (waveform sine/saw/square/file) on a trigger

#### SW architecture

☐ Python class diagram:

## **Implementations**

- C executables

- Uses NI PXI-6259 Linux Device Driver (Cosylab)

- EPICS device support

- Asyn based

- NDS based

- ☐ LabVIEW

- NI-DAQmx driver supports the full functionality

- start an IOC in LabVIEW (using CA Lab by BESSY)

#### **Test scenarios**

- ☐ Generate on TB, acquire on SUT, check

- ☐ Generate on SUT, acquire on TB, check

- ☐ Generate on SUT, acquire on SUT

```

nn COSYLAB

```

```

☐class TestNI6259 (UnitTestBed):

9

# create SUT and Testbed

TB = testbed()

10

11

SUT = sut()

12

13

@classmethod

14

def setUpClass(self):

15

# setup SUT

self.SUT.server = "10.5.3.93"

16

17

self.SUT.username = "bled"

18

# setup TESTBED

19

self.TB.server = "10.5.3.175"

20

self.TB.username = "codac-dev"

21

22

def setUp(self):

23

self.TB.resetDevice()

24

self.SUT.resetDevice()

25

26

'''TESTING aio (static)'''

27

def test aio static(self):

35

36

'''TESTING dio (static)'''

def test dio static(self):

37

45

46

'''TESTING aio (waveform)'''

47

def test aio wf(self):

67

68

@classmethod

69

def tearDownClass(self):

self.TB.resetDevice()

70

71

self.SUT.resetDevice()

72

del self.TB

73

del self.SUT

```

## 10 test aio static

```

'''TESTING aio (static)'''

26

def test aio_static(self):

2.7

28

# generate constant voltage on the TB, aol

29

Vreg = random.uniform(-10,10)

30

self.TB.analogOutputStatic(1, Vreg)

31

# acquire voltage on the SUT, ai0

32

Vact = self.SUT.analogInputStatic(0)

33

# compare the results

34

self.assertAlmostEqual(Vact, Vreq, 1)

35

```

## 11 test\_dio\_static

```

'''TESTING dio (static)'''

36

37

def test dio static(self):

# set do0 on the TB to a random state

38

39

STreq = random.randint(0,1)

40

self.TB.digitalOutput(0,STreq)

41

# get di32 on the SUT

42

STact = self.SUT.digitalInput(33)

43

# compare the results

44

self.assertEqual(STreq,STact)

45

```

```

'''TESTING aio (waveform)'''

46

def test aio wf(self):

sample rate = 500

48

nsamples = 1024

49

ampl = 2

50

51

offs = 1

phase = 1

52

53

# delta = [offset, ampl, freq, phase] mV

delta = [0.05, 0.05, 0.05, 0.05]

54

# create a waveform

wf out = self.TB.generateWaveform(sample rate, nsamples, "sine", ampl, offs, phase)

56

# on a rising edge of pfil line generate wf on aol

57

self.TB.analogOutputOnTriggerWF(1, sample rate, "pfi1")

58

# on a rising edge of pfil line acquire wf on ai0

59

self.SUT.analogInputOnTrigger(0, sample rate, nsamples, "pfi1")

60

# trigger pfil

self.TB.digitalOutput(0,1)

62

# get waveform from SUT

63

data = self.SUT.getAcquiredWaveform()

64

# compare the results

65

66

self.assertAlmostEqualSine(sample rate, nsamples, ampl, offs, phase, wf out, data, delta)

67

```

Your **TRUSTED** Control System Partner

This project has received funding from the European Union's Seventh Framework Programme for research, technological development and demonstration under grant agreement no 289485.

## **THANK YOU!**

**Pavel Maslov**

**COSYLAB**

Tel.: +386 406 32 571

Web: www.cosylab.com