# LANSCE DRIFT TUBE LINAC WATER CONTROL SYSTEM REFURBISHMENT\*

P. Marroquin, J. Bernardin, J. Gioia, J. Ortiz, LANL, Los Alamos, NM 87545, U.S.A.

#### Abstract

There are several refurbishment projects underway at the Los Alamos National Laboratory LANSCE linear accelerator. Systems involved are: RF, water cooling, networks, diagnostics, timing, controls, etc. The Drift Tube Linac (DTL) portion of the accelerator consists of four DTL tanks, each with three independent water control systems. The systems are about 40 years old, use outdated and non-replaceable equipment and NIM bin control modules, are beyond their design life and provide unstable temperature control. Insufficient instrumentation and documentation further complicate efforts at maintaining system performance. Detailed design of the replacement cooling systems is currently in progress. Previous design experience on the SNS accelerator water cooling systems will be leveraged, see the SNS DTL FDR [1]. Plans call for replacement of water piping, manifolds, pumps, valves, mix tanks, instrumentation (flow, pressure and temperature) and control system hardware and software. This presentation will focus on the control system design with specific attention on planned use of the National Instruments Compact RIO platform with the Experimental Physics and Industrial Control System (EPICS) software toolkit.

# **OVERVIEW**

# LANSCE Drift Tube Linac Water Cooling Systems

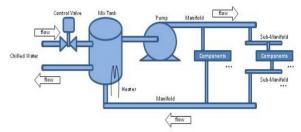

The LANSCE Drift Tube Linac consists of 4 tanks. Each tank is supported by three water cooling systems: drift tube, tank wall, and quad magnet.

Currently each water cooling system includes:

- a mix tank

- water supply and return manifolds

- water sub-manifolds

- manually operated isolation valves

- an automated valve to control the amount of chilled water flowing into the mix tank

- an automated water pump to maintain flow/pressure in the cooling loop

- an automated heater to add heat to the water when the Radio Frequency (RF) System is off

- temperature sensors read by the control system as control inputs for the valve, pump and heater

- pressure, temperature and water flow sensors read by the control system for sub-manifold monitoring

**Accelerator Technology**

Figure 1: Drift tube linac water cooling system.

• water flow switches, read by the control system, for monitoring low water flows to individual Linac components

# Refurbishment Plan

An engineering team has been assembled to design all mechanical, electrical, instrumentation and control aspects of the water systems. The planned approach is, in this fiscal year FY 2011, to complete the water cooling system design for the DTL tank which would improve accelerator operations most significantly. Then duplicate and fit the design to the other three tanks in fiscal year 2012. Procurement and assembly for the first tank are also planned for FY 2012. Installation, testing, commissioning and release for production are planned for early calendar year 2013.

Although considerable and notable progress has been made on the mechanical engineering aspects of this project the focus of this paper is on the instrumentation and controls system portion, or more specifically the control system automation hardware and software design.

A water system test stand is under construction which will be used to validate instrumentation selection; automation control system hardware and software platforms, controls methodology, closed and open loop logic schemes, as well as interlock and alarm monitoring, responses and actions. Engineering solutions to hardware layouts, processor load balancing, interfaces and integration into the LANSCE Control System (LCS) will also be tested and proven.

# **CONTROL SYSTEM DESIGN OVERVIEW**

The new control system will consist of one programmable controller per tank to include control and monitoring of the three water cooling loops, effectively combining and enhancing the capabilities of the old control systems One new control system will simultaneously monitor and control three separate water cooling circuits on a single tank. The National Instruments (NI) Compact RIO (cRIO) is the selected programmable automation controller. The cRIO includes

<sup>\*</sup> Work performed under the auspices of the U.S. Department of Energy, under contract DE-AC52-06NA25396 LANL LA-UR-11-10230

input/output (I/O) modules, a field programmable gate array (FPGA) for I/O signal processing and an embedded real time processor running as an EPICS input/output controller (IOC).

The FPGA will be programmed to perform proportional, integral and derivative (PID) closed loop control of the valves and pumps to maintain desired water temperature and flow rate setpoints, respectively. The IOC will be programmed to perform alarm limit checking on individual inputs and interlock monitoring and their corresponding automatic control actions. The IOC's Channel Access server will publish all variables on the LCS network.

The cRIO FPGA's will be programmed with NI LabVIEW running on a Windows computer on the LANSCE Control System network.

The embedded IOC on the cRIO will boot from a designated vxWorks boot server on the LCS network.

Engineering control screens will be developed using the EPICS extensible display manager (EDM) and be available to all LCS workstations on the LCS network.

All EPICS process variables (PV) will be available to other IOCs, applications, control screens, archivers, etc on the LCS network for further processing, inputs to analysis applications, presentation on plots or trends, archiving, etc.

### **CONTROL SYSTEM HARDWARE**

#### NI cRIO

The NI cRIO is a compact re-configurable input output platform. The 8 slot chassis incorporates a reconfigurable FPGA for stand-alone embedded processing with direct access to low level input/output hardware modules. The platform also features a real-time controller interfaced to the FPGA via PCI. For this specific application the real time controller will be running the Wind River real-time operating system VxWorks and EPICS IOC software.

The specific chassis selected for this project is the NI cRIO-9118 8-slot Virtex-5 LX 110 Reconfigurable Chassis for cRIO. The Virtex-5 LX 110 FPGAs are the largest and fastest (69,120 6 input LUTS, 4608 kbits of block RAM) cRIO FPGA that NI currently offers.

The selected real-time processor is the cRIO-9024 Real-Time PowerPC Controller for cRIO, 800 MHz 4GB, \$512 MB DRAM. The 9024 is a high performance controller with 2 gigabit Ethernet ports, 1 USB port and 1

Figure 2: NI real time controller and FPGA chassis.

#### cRIO I/O Modules

An assortment of input and output signals is required for each water loop. Analog inputs for pressure and flow

measurements and pump speed and valve position readbacks will be 4-20mA signals and for temperatures, resistance temperature detectors (RTD) will be used. Analog outputs for pump speed and valve positioning will also be 4-20mA signals. Digital inputs for a variety of status and interlock signals and digital outputs for outbound interlocks and enable/disable commands are also required.

| Table 1: | Selected NI I/O Modules |

|----------|-------------------------|

|----------|-------------------------|

| I/O Module | Description                |

|------------|----------------------------|

| NI 9425    | DI, 32 chan, 24VDC sinking |

| NI 9485    | DO, 8 chan, relay          |

| NI 9203    | AI, 8 chan, 0-20 mA        |

| NI 9217    | AI, 4 chan, RTD            |

| NI 9265    | AO, 4 chan, 0-20 mA        |

Figure 3: NI cRIO with I/O modules installed.

# **CONTROL SYSTEM SOFTWARE**

#### **EPICS** in Brief

EPICS is the Experimental Physics and Industrial Control System. It is a set of software tools and applications for building distributed control systems on a variety of operating systems and platforms and supporting a large number of devices and communication protocols.

Figure 4: EPICS overview.

#### Software

Software will be distributed amongst three primary components: FPGA, IOC and EPICS server. The operator will interface with the system via operator control screens on local LCS workstations. EPICS Channel Access Security will be implemented to limit control variable changes to this account.

All software source code will be submitted to and maintained in the LANSCE Control System software configuration control repository.

FPGA software will be written using NI LabVIEW. The software will be developed on a Windows system. and then it will be compiled, optimized and downloaded

> Accelerator Technology **Tech 20: Infrastructure**

to the target FPGA. The program will be retained on the FPGA.

The top level FPGA VI (virtual instrument) will call sub VI's to perform the following functions:

- Read, filter and convert input channels to engineering units (AI) and states (DI)

- Read operator command and setpoint requests and incoming interlock data (via IOC/CA)

- Cycle valve control (logic+PID), pump control (logic+PID), heater control in parallel

- Write and convert output channels

- Write monitored data and control readbacks, AO and DO for pick up by the IOC

The cRIO real-time controller will boot VxWorks. EPICS IOCcore will be installed along with record databases and sequencer programs. Record databases define EPICS channel configurations An EPICS channel is referred to as a PV (process variable).

The EPICS IOC will perform the functions;

- Execute an EPICS Channel Access (CA) Server

- Scan all database records per configured scan rates

- Range check operator entered parameters

- Interface to FPGA via the LabVIEW Real Time Controller shared memory

- Perform calculations and check inputs for threshold limits (i.e. flow setpoints on flowmeters)

- Check interlocks (trips and permissives) and take appropriate action (set internal variable status, set external status/interlocks/trips, etc.)

- Create monitors for CA clients

#### Logic

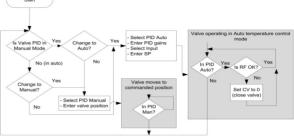

All control elements in each of the three pump loops will be executed concurrently. The pump PID and encapsulating control logic, the valve PID and encapsulating control logic and the heater control logic would each execute in parallel and independently. The following diagrams describe each in detail.

Figure 5: Pump logic diagram.

Figure 6: Valve logic diagram.

These new control features (hardware and software) along with new mechanical equipment, will dramatically improve water flow stability and temperature control.

#### Interlocks and Alarms

Permissives and interlocks have been identified to prevent turn on or shut down the pumps. In general low water flow and large differences between inlet and outlet water flows indicate leaks. Pump equipment over-heating or operators pressing e-stops will also shut off pumps. Other off-normal conditions in the major category will shut off the heater as well.

All measurements are continuously checked for HIHI, HI, LO and LOLO alarms. Alarm status are distributed to the LCS Control system via EPICS. Water system status conditions are also transmitted via the network for other systems to pick up and take action on.

#### **SUMMARY**

Refurbishment of the DTL Water Cooling Systems, currently in design but soon to be installed, will result not only in a vast improvement in measurement and control of the water systems but contribute towards improved operational efficiency and increased beam production of the LANSCE accelerator.

#### REFERENCES

- J. Bernardin, et.al, "Spallation Neutron Source Drift Tube Linac Water Cooling and Resonance Control System Final Design Report", SNS-104020500-DE0001-R01, LANL LAUR-02-1213, April 2001

- [2] Treml, C., et.al, "Resonance Control Cooling System for a Prototype Coupled Cavity Linac", Proceedings to the 8<sup>th</sup> International Conference on Accelerator and Large Experimental Physics Control Systems, WEPo76, San Jose, CA

- [3] Marroquin, P., "Integrating Externally Developed Systems For SNS Linac Cooling and Vacuum", ICALEPCS 2001, TUAP063, November 2001, San Jose, CA

- [4] Bjorklund, E., et.al, "Running EPICS on the NI compact RIO platform", National Instruments Big Physics Symposium, August 2009, Austin, TX

- [5] Bjorklund, E., et.al, "Experience running embedded EPICS NI compactRIO", EPICS Collaboration Meeting, October 2010, Upton, NY