## **RAPID CONTROL PROTOTYPING TOOL FOR THE SIRIUS HIGH-DYNAMIC DCM CONTROL SYSTEM**

<u>G. B. Z. L. Moreno</u>\*, R. M. Caliari, R. R. Geraldes, M. A. L. Moraes LNLS, Campinas, Brazil \*gabriel.moreno@lnls.br

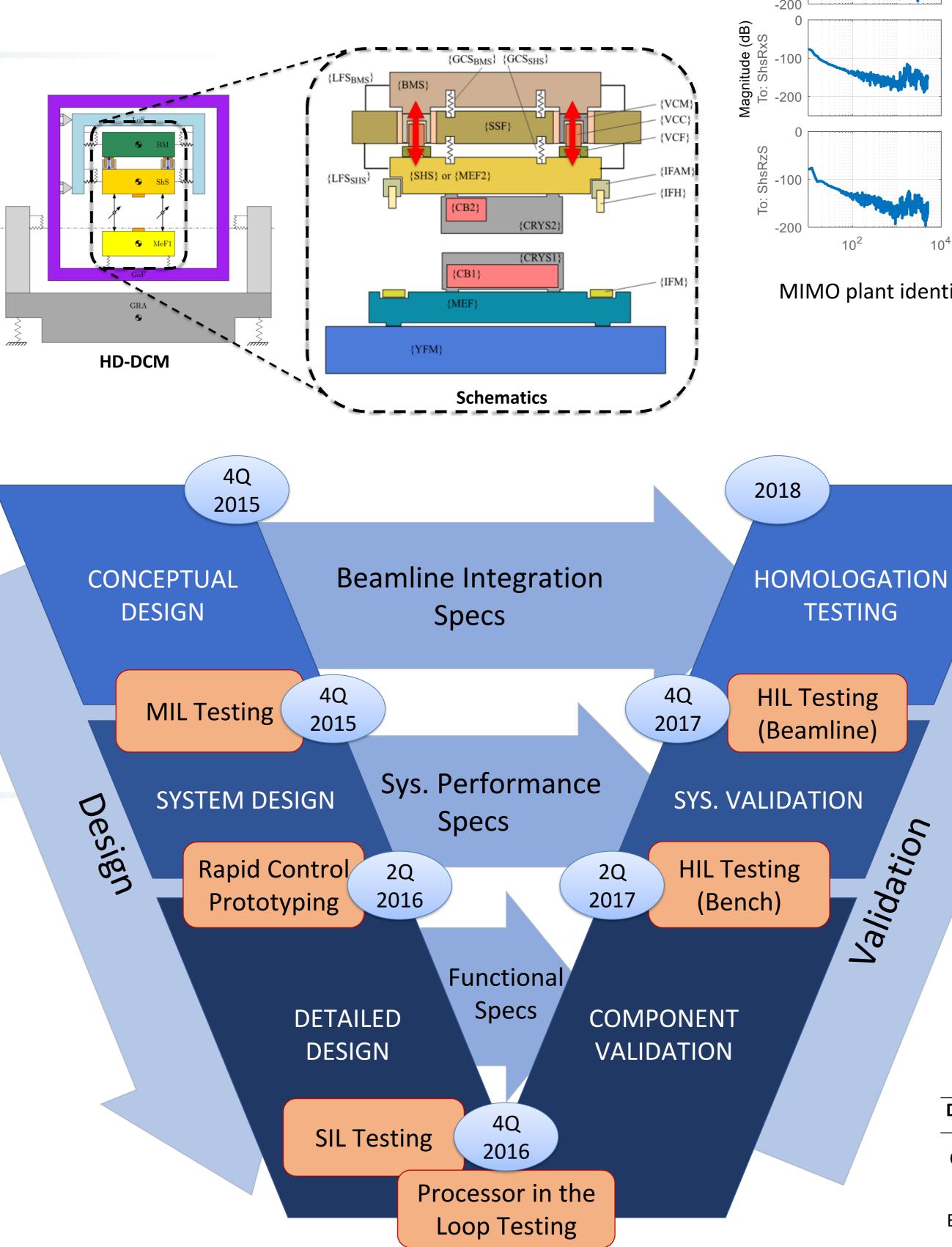

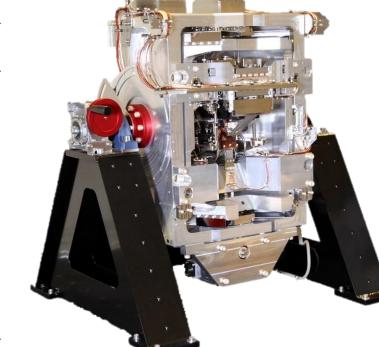

# The monochromator is known to be one of the most critical optical elements of a synchrotron beamline. It directly affects the beam quality with respect to power load variation, and vibration sources. To identify and ensure sufficient control of the dynamic behavior of all subcomponents in the prototype, an

#### Abstract

#### Introduction

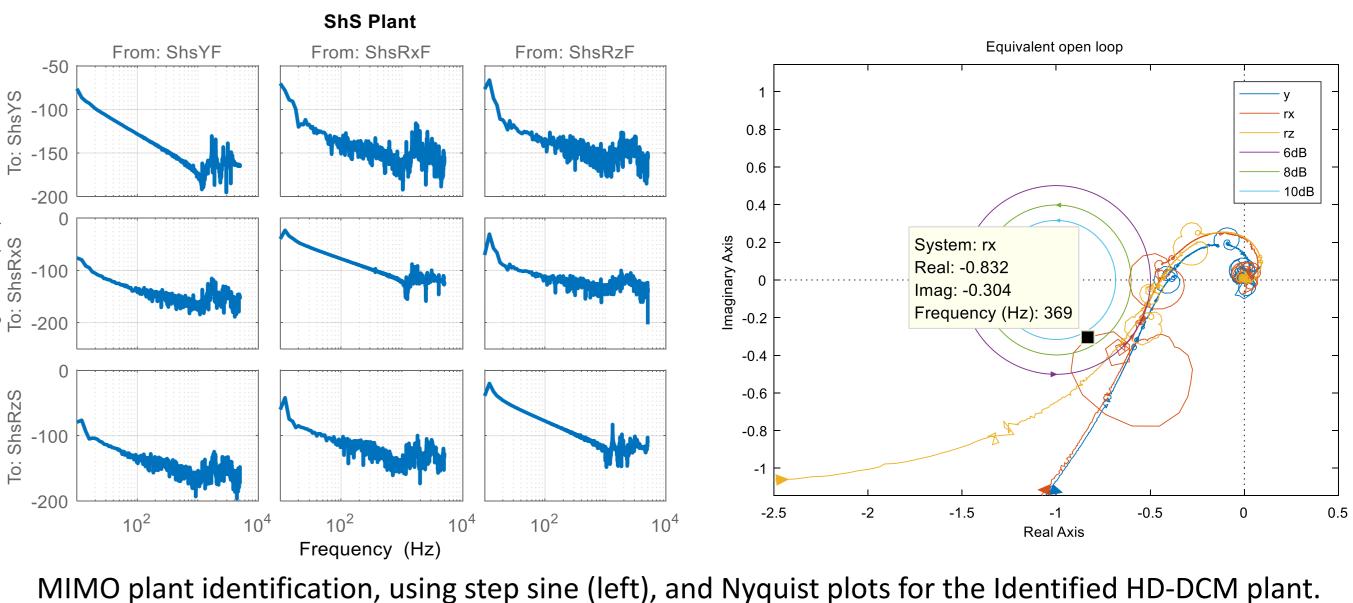

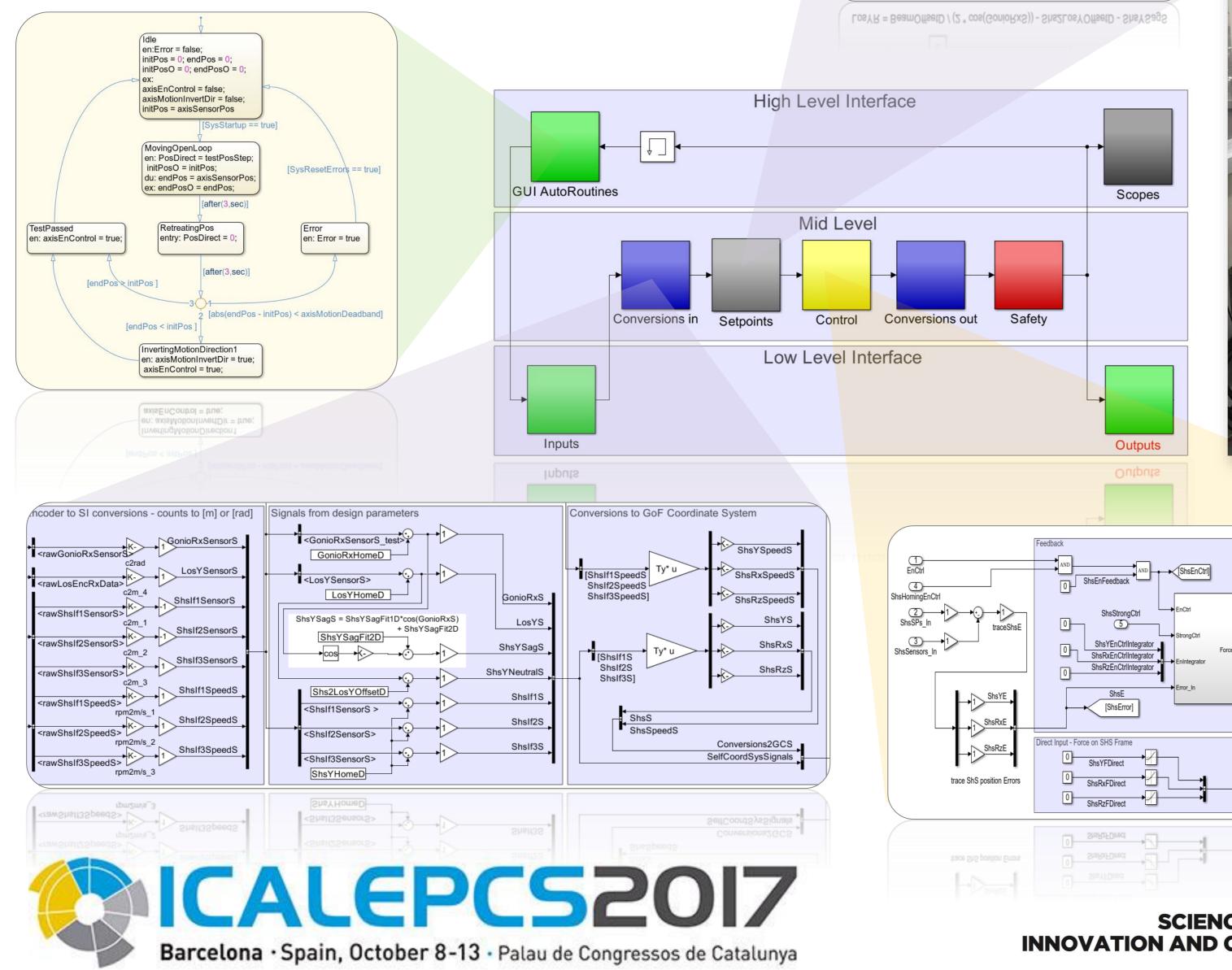

energy and position, demanding high stability performance, and fine position control. The new high-dynamic double-crystal monochromator (HD-DCM) [1-5], prototyped at the Brazilian Synchrotron Light Laboratory (LNLS), was designed for the future X-Ray undulator and superbend beamlines of Sirius, the new Brazilian 4th generation synchrotron [6-8]. At this kind of machine, the demand for stability is even higher and conflicts with factors such as high power loads, implementation in MATLAB / Simulink Real-Time environment in a Speedgoat Real-Time Performance Machine [9] was developed. This approach enables rapid prototyping, by allowing a shared environment for system modeling and testing. The tool was developed in a modular architecture aiming at a practical model iteration and platform migration to beamline controllers, which can prove portability and scalability features.

#### **System Validation**

This work presents a Rapid Control Prototyping (RCP) tool, used for designing and testing the new High-Dynamic Double-Crystal Monochromator. This tool was implemented with the objective of speeding up control design and testing phases, considering the upcoming high demand for designing and commissioning multiple high-end systems in a short time for Sirius. Its architecture and parametrization focuses on a smooth migration to a standard control platform, chosen for advanced applications at Sirius beamlines [10].

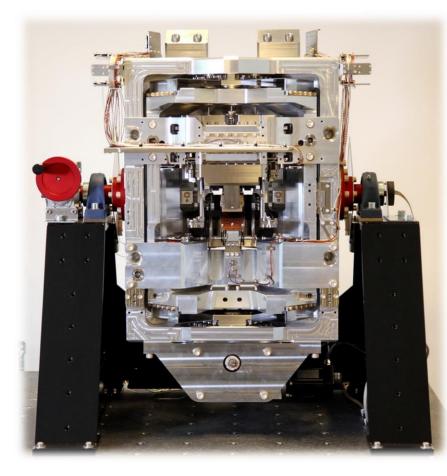

### **High-Dynamic DCM Concept**

□ High-Dynamic Core Tests

(performed mid 2017)

✓ 0.9 nm rel. gap error\*

✓ in-vacuum cryocooled

of 2017.

✓ 9.2nrad rel. pitch/roll error\*

system expected by the end

Completely reviewed version of usual DCM Design ✓ Control-Oriented Mechanical Design ✓ Balance-Mass Concept ✓ Contactless Actuators ✓ Leaf-Springs ✓ Thermal Control

|                        | Bragg<br>Angle        | Long<br>Stroke       | Short<br>Stroke | Thermal<br>Control |

|------------------------|-----------------------|----------------------|-----------------|--------------------|

| Actuator Type          | Torque<br>Motor       | Stepper<br>or Servo  | Voice-Coils     | Foil<br>Heaters    |

| Sensor Type            | Rot. Incr.<br>Encoder | Lin. Abs.<br>Encoder | IFM             | RTDs               |

| Feedback<br>Resolution | 50nrad                | 5nm                  | 0.1nm/<br>1nrad | <10mK              |

| Stability target*      | <0.8µrad              | N/A                  | <10nrad         | <50mK              |

| Closed-Loop BW         | 35 Hz                 | 20 Hz                | >250 Hz         | 0.1 Hz             |

| Feedback<br>Sampling   | 10 kHz                | 10 kHz               | 20 kHz          | 20 Hz              |

'in-position stability, RIVIS values integrated up to 2500 Hz.

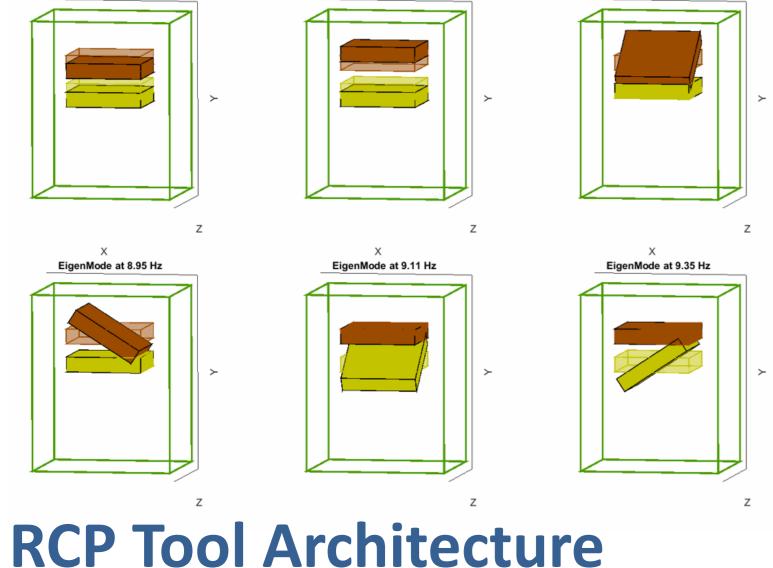

#### **Model Based Design**

| х                    | X                    | х                    |

|----------------------|----------------------|----------------------|

| EigenMode at 5.94 Hz | EigenMode at 5.94 Hz | EigenMode at 8.95 Hz |

.........

→ 1 ShsRzF

trace ShS Forces and Torques

ShsContOut J

ShsNoise

ShsFDirect

ShsFDirect

**MINISTRY OF**

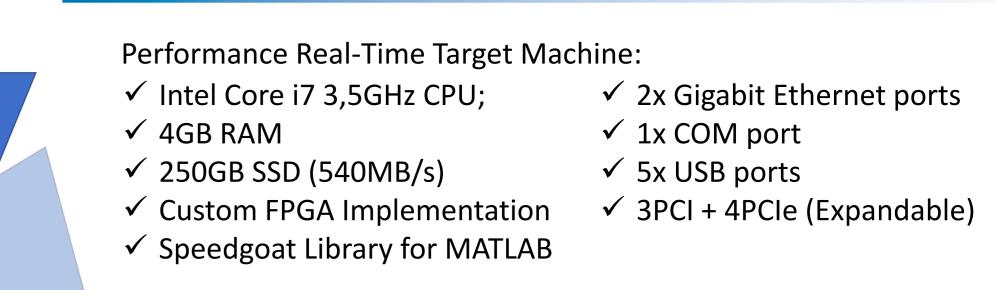

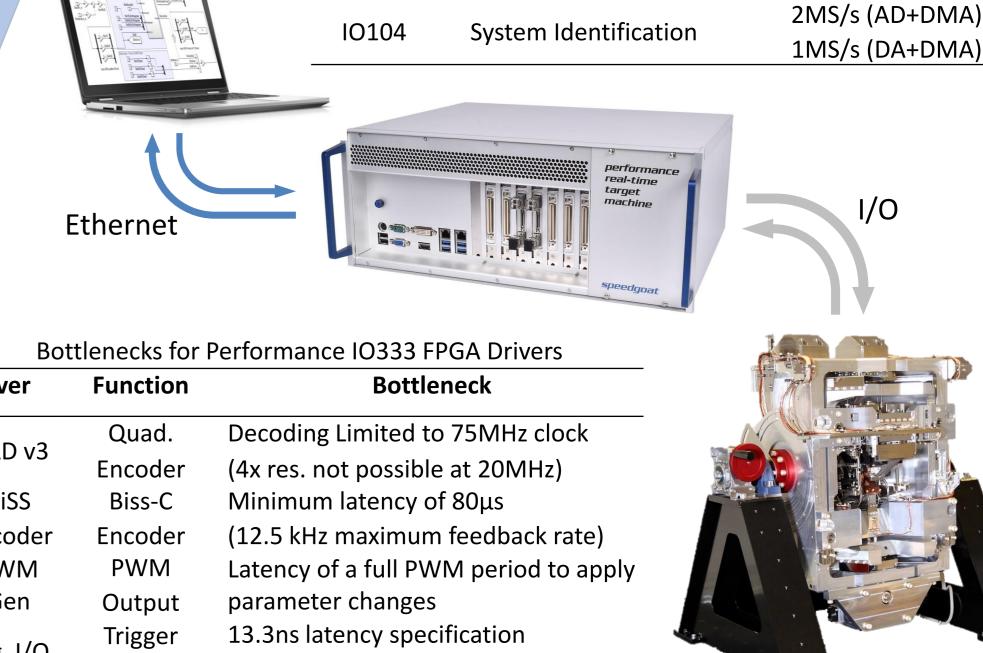

#### **RCP Hardware Performance**

| Hardware | Function                | Maximum Rates                      |

|----------|-------------------------|------------------------------------|

| 10333    | Digital I/O (with FPGA) | Applic. Dependent<br>(75MHz Clock) |

| IO107    | Analog Output           | ~450kHz update                     |

| 10171    | <b>RTD Sensing</b>      | ~45Hz update                       |

|          |                         | 2NAS/s(AD+DNAA)                    |

| Bot      | tlenecks for | Performance IO333 FPGA Drivers        |  |

|----------|--------------|---------------------------------------|--|

| Driver   | Function     | Bottleneck                            |  |

| QAD v3   | Quad.        | Decoding Limited to 75MHz clock       |  |

|          | Encoder      | (4x res. not possible at 20MHz)       |  |

| BiSS     | Biss-C       | Minimum latency of 80µs               |  |

| Encoder  | Encoder      | (12.5 kHz maximum feedback rate)      |  |

| PWM      | PWM          | Latency of a full PWM period to apply |  |

| Gen      | Output       | parameter changes                     |  |

| Dig. I/O | Trigger      | 13.3ns latency specification          |  |

|          | Output       | (75MHz FPGA Clock)                    |  |

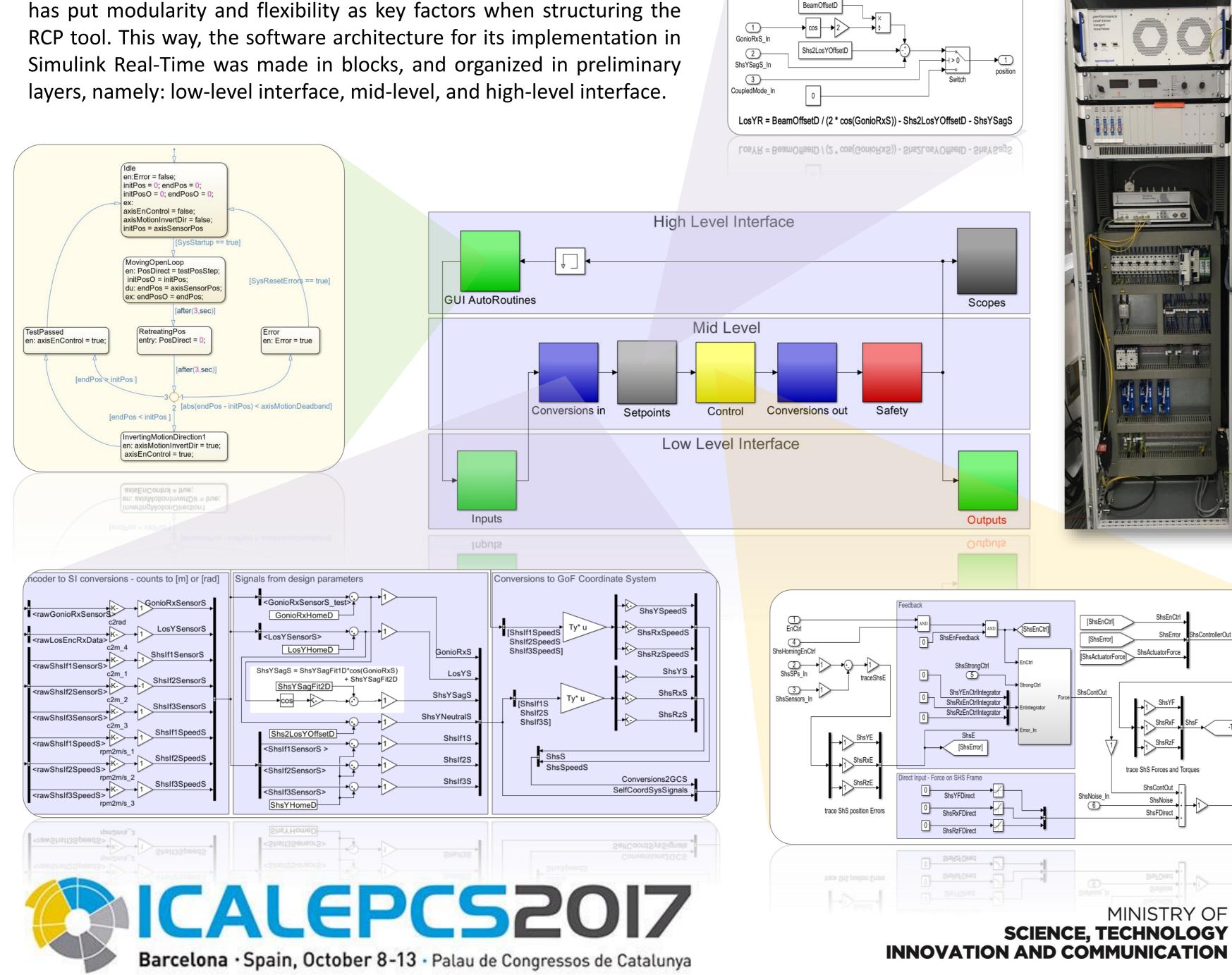

The demand for quickly testing the HD-DCM system and future projects has put modularity and flexibility as key factors when structuring the

#### Conclusion

The RCP tool implemented in Speedgoat's xPC target accelerated the design and testing phases, permitting the model and hardware tests to coexist in the same platform. The proposed architecture modularity and flexibility, allows parameters and even complete structures to be directly exported from the Simulink model to the standard beamline control platform, which has a more advantageous cost-benefit relation. Indeed, once the development of the HD-DCM is finished, its final control plat-form will take over and the RCP tool will be modified for a new system.

### Acknowledgement

The authors would like to gratefully acknowledge the funding by the Brazilian Ministry of Science, Technology, Innovation and Communication and the contribution of the LNLS team, the MI-Partners team

and those of the synchrotron community who directly or indirectly built the path to this development.

#### References

[1]R. R. Geraldes, R. M. Caliari, and M. S. Silva, "Instrumento para movimentação e posicionamento de elementos ópticos com resolução e estabilidade mecânica nanométricas em linhas de luz," PCT/BR2017/050262, Patent Application, 2017.

[2]R. R. Geraldes et al., "THE NEW HIGH DYNAMICS DCM FOR SIRIUS," Proc. of MEDSI 2016, pp. 141-146, 2016.

[3]R. M. Caliari, M. A. L. Moraes, G. B. Z. L. Moreno, R. R. Geraldes, T. Ruijl, and R. Schneider, "System identification and control for the Sirius high-dynamic DCM," Proc. of ICALEPCS'17, 2017.

[4]R. R. Geraldes, R. M. Caliari, G. B. Z. L. Moreno, M. J. C. Ronde, T. A. M. Ruijl, and R. M. Schneider, "Mechatronics concepts for the new highdynamics DCM for SIRIUS." Proc. of MEDSI 2016, pp. 44-47, 2016.

[5]M. S. Silva, R. R. Geraldes, A. Gilmour, T. A. M. Ruijl, R. M. Schneider, and M. I. Partners, "Thermal management and crystal clamping concepts for the new high-dynamics DCM for Sirius," Proc. of MEDSI 2016, pp. 194-197, 2016.

[6]A. R. D. Rodrigues et al., "Sirius Status Report," Proc. of IPAC 2016, pp. 2811–2814, 2016.

[7]L. Liu, F. H. de Sá, and X. R. Resende, "A new optics for Sirius," Proc. of IPAC 2016, pp. 3413–3415, 2016.

[8]R. Hettel, "DLSR design and plans: An international overview," J. Synchrotron Radiat., vol. 21, no. 5, pp. 843–855, 2014. [9]Speedgoat GmbH, "Speedgoat Solutions and Use," 2011.

[10] M. A. L. Moraes, H. D. Almeida, R. M. Caliari, R. R. Geraldes, G. B. Z. L. Moreno, and J. R. Piton, "A control architecture proposal for Sirius beamlines," Proc. of ICALEPCS'17, 2017.

[11] MathWorks, "Perform Hardware-in-the-Loop Simulation with MATLAB and Simulink to Test and Validate Control Algorithms," p. 6, 2016. [12]P. Lambrechts, M. Boerlage, and M. Steinbuch, "Trajectory planning and feedforward design for electromechanical motion systems," Control Eng. Pract., vol. 13, no. 2, pp. 145–157, 2005.