# Disruptor Using High Performance, Low Latency Technology in the CERN Control System

**ICALEPCS 2015**

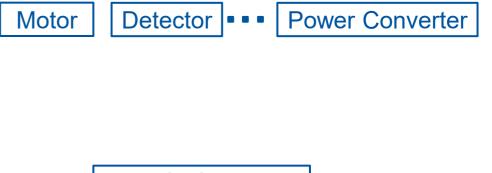

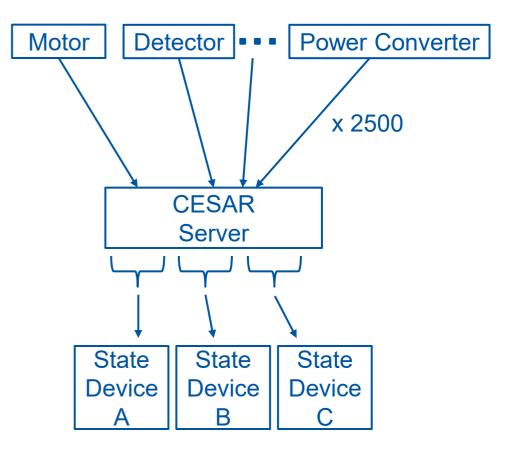

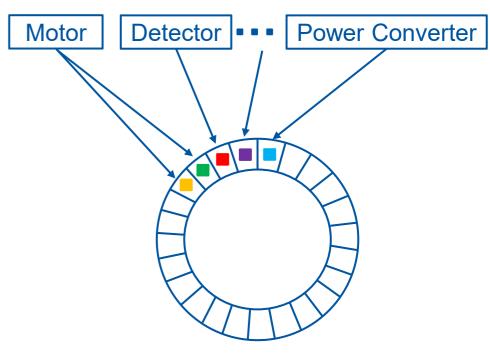

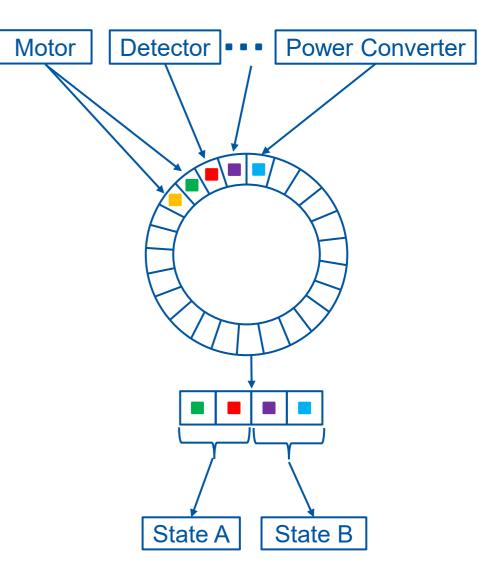

CESAR is used to control the devices in CERN experimental areas

- CESAR is used to control the devices in CERN experimental areas

- These devices produce 2500 event streams

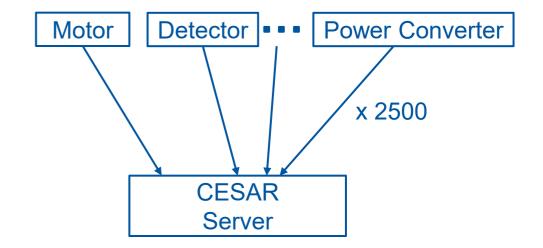

- CESAR is used to control the devices in CERN experimental areas

- These devices produce 2500 event streams

- The business logic on the CESAR server combines the data coming from these streams to calculate device states

- CESAR is used to control the devices in CERN experimental areas

- These devices produce 2500 event streams

- The business logic on the CESAR server combines the data coming from these streams to calculate device states

- This concurrent processing must be properly synchronized

### What happens when all flows converge?

Created by LMAX, a trading company, to build a high performance Forex exchange

- Created by LMAX, a trading company, to build a high performance Forex exchange

- Is the result of different trials and errors

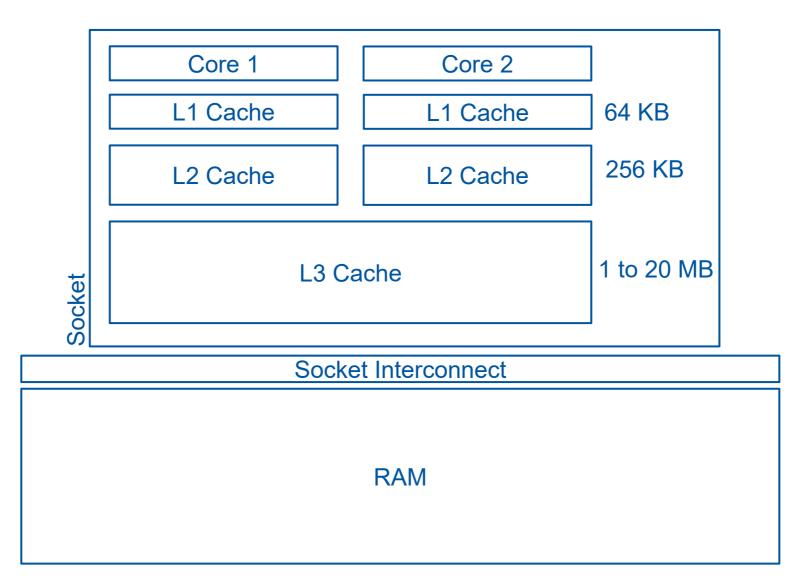

- Created by LMAX, a trading company, to build a high performance Forex exchange

- Is the result of different trials and errors

- Challenges the idea that "CPUs are not getting any faster"

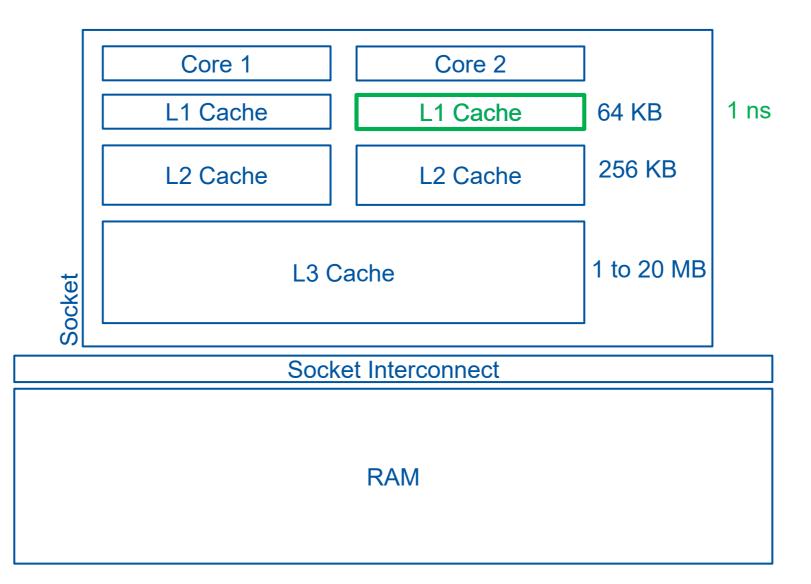

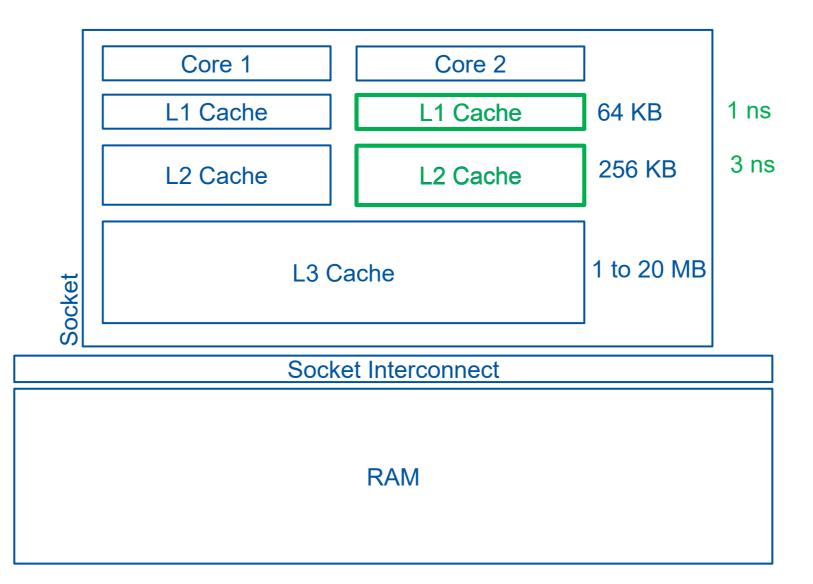

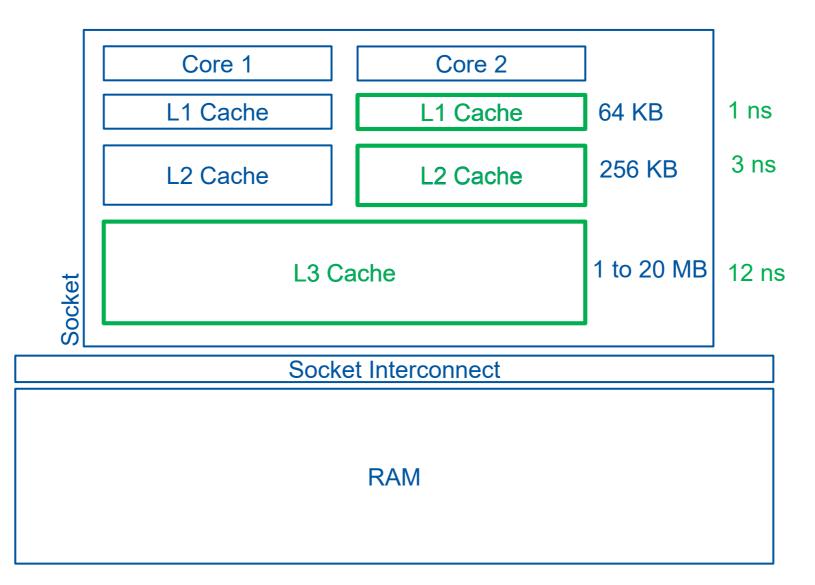

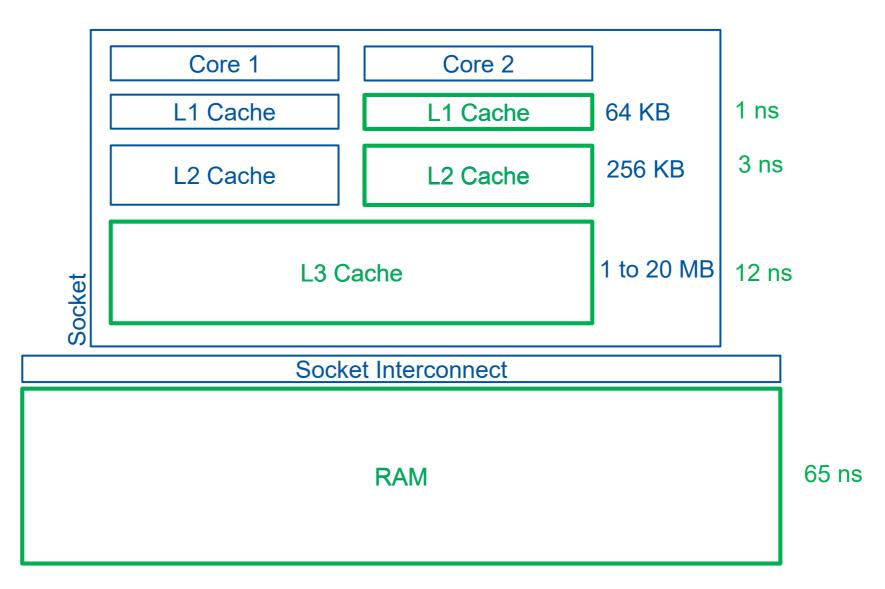

- Created by LMAX, a trading company, to build a high performance Forex exchange

- Is the result of different trials and errors

- Challenges the idea that "CPUs are not getting any faster"

- Designed to take advantage of the architecture of modern CPUs, following the concept of "mechanical sympathy"

21/10/2015

21/10/2015

21/10/2015

21/10/2015

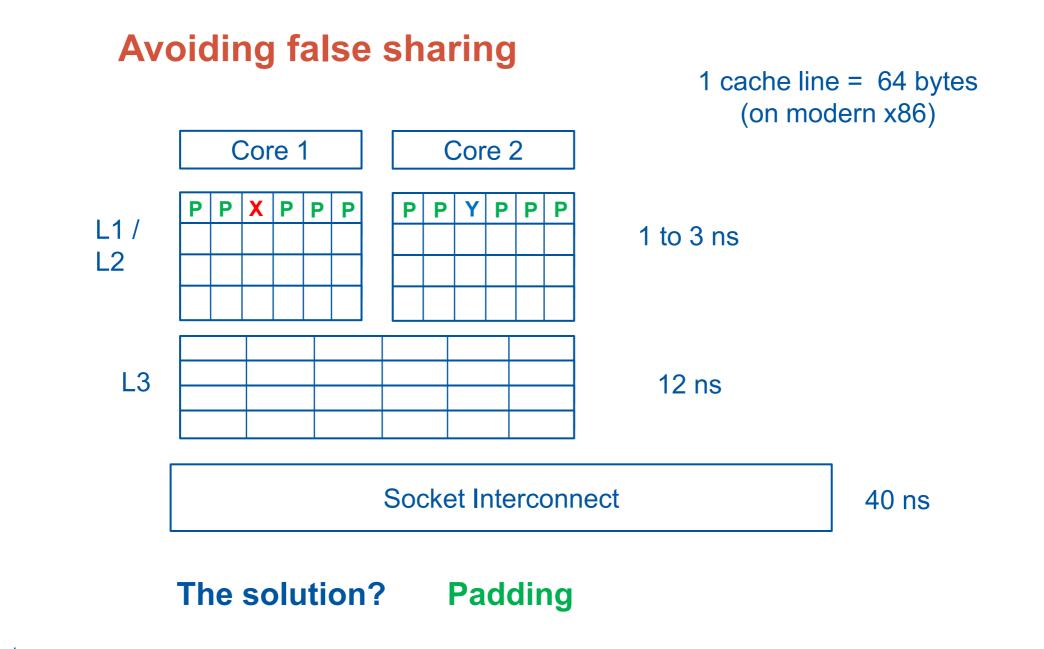

#### The solution?

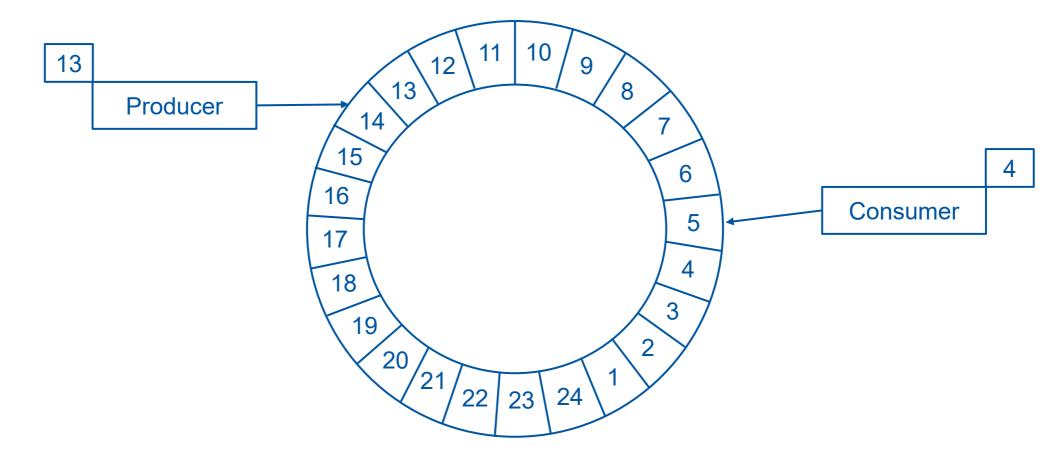

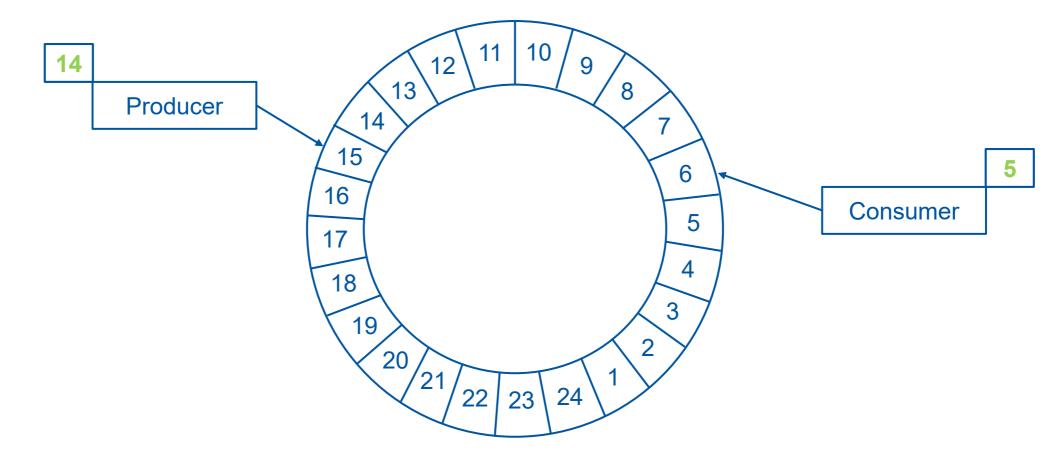

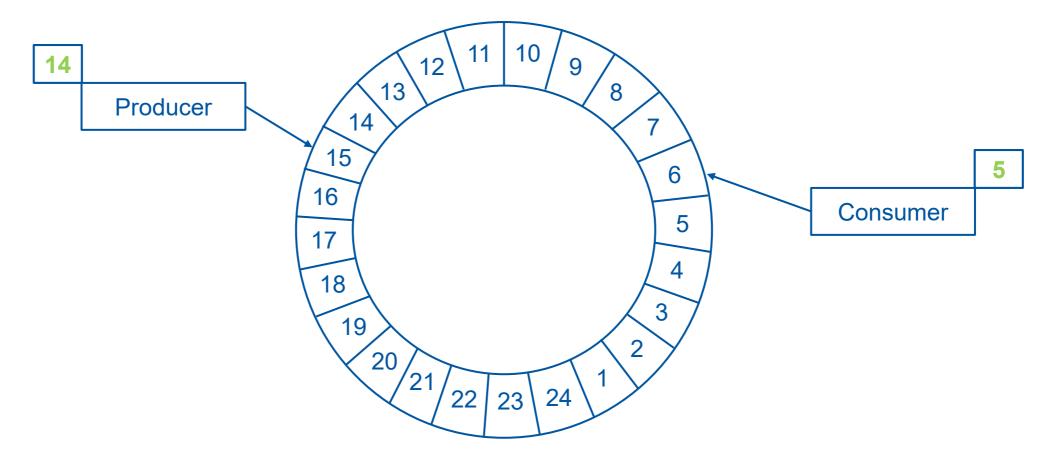

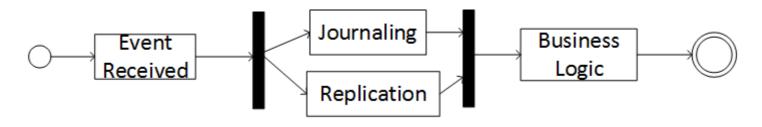

2 - Disruptor architecture

- What is it?

- → Can be viewed as a very efficient FIFO bounded queue

- → A data structure to pass data between threads, designed to avoid contention

• Represented internally as an array  $\rightarrow$  caches gets prefetched

- Represented internally as an array  $\rightarrow$  caches gets prefetched

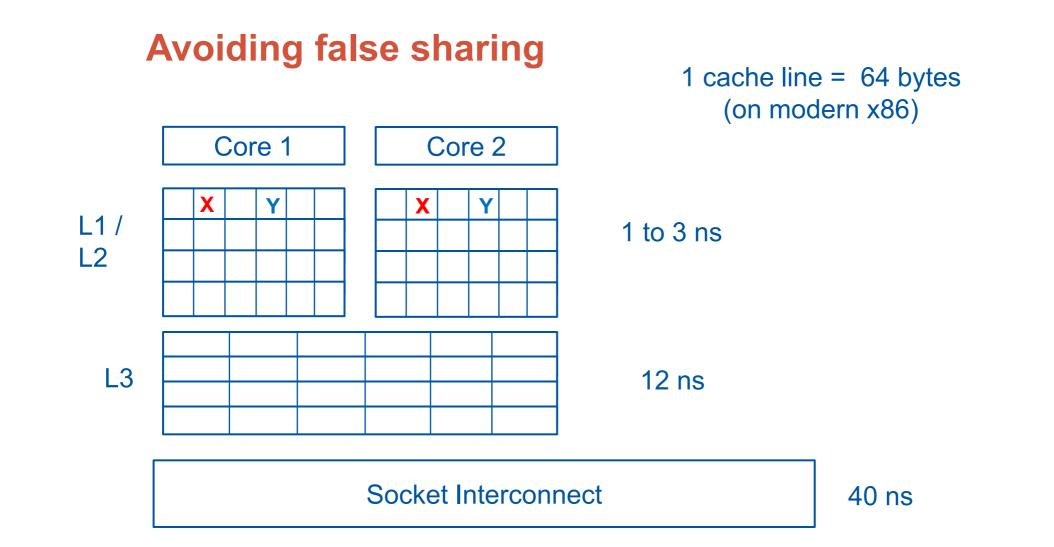

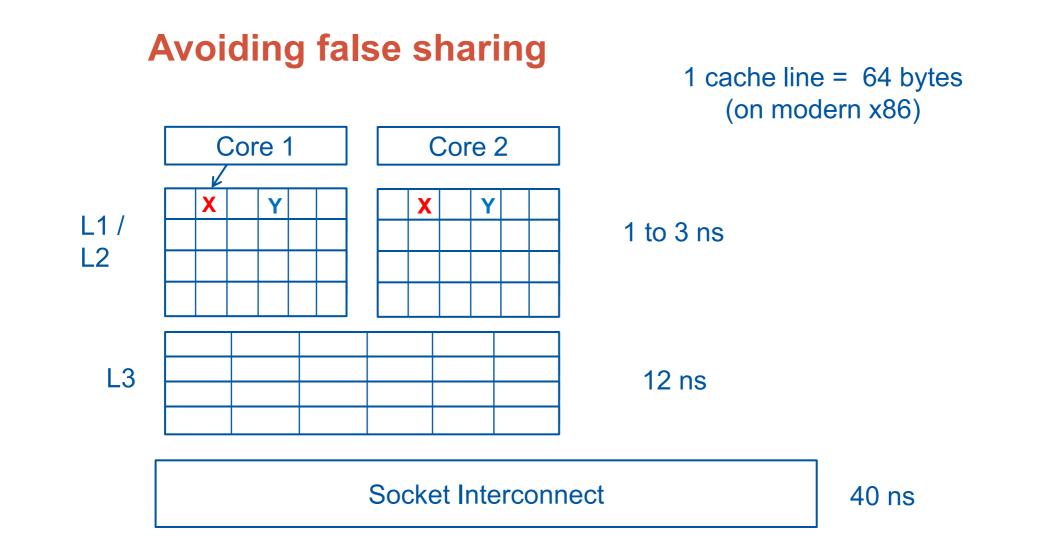

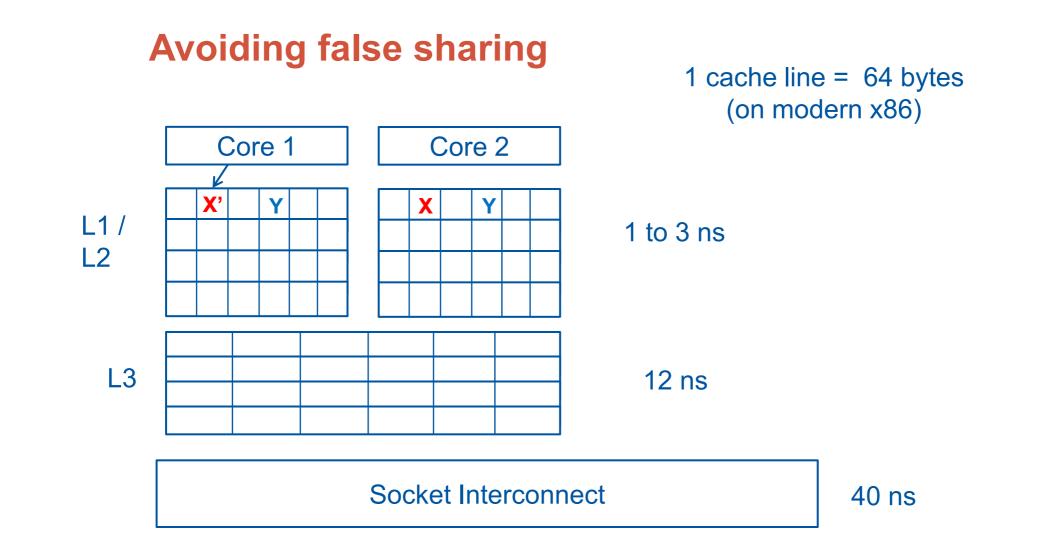

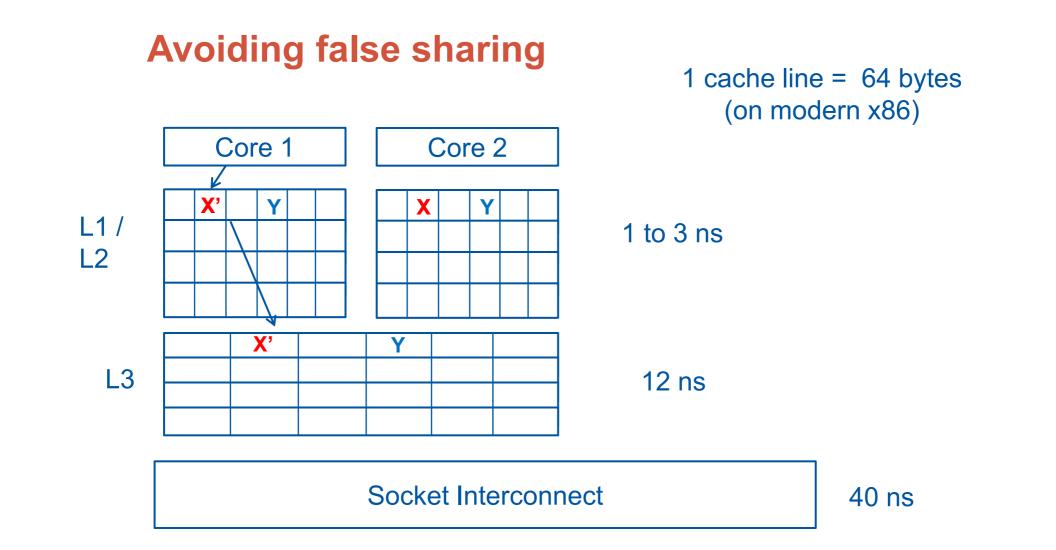

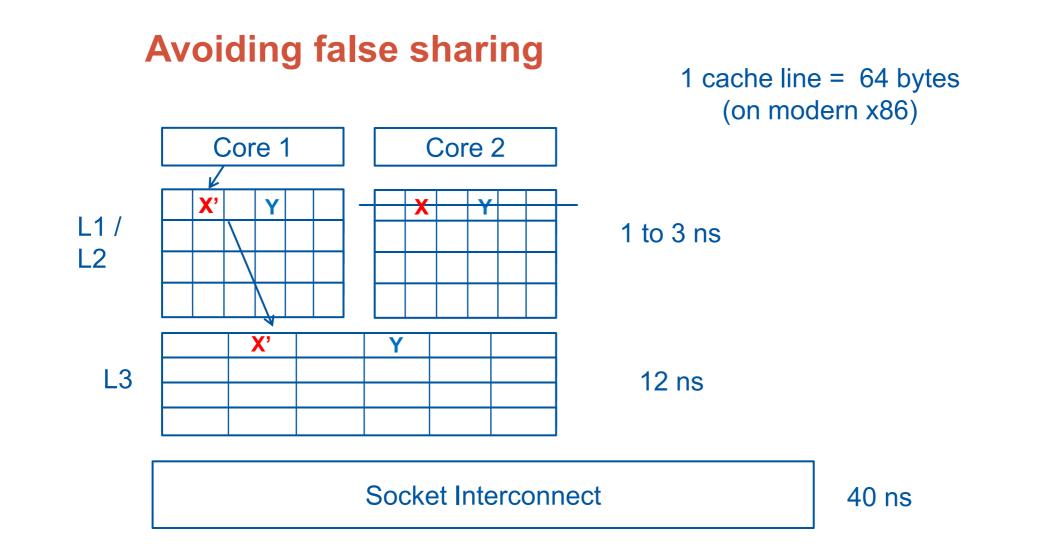

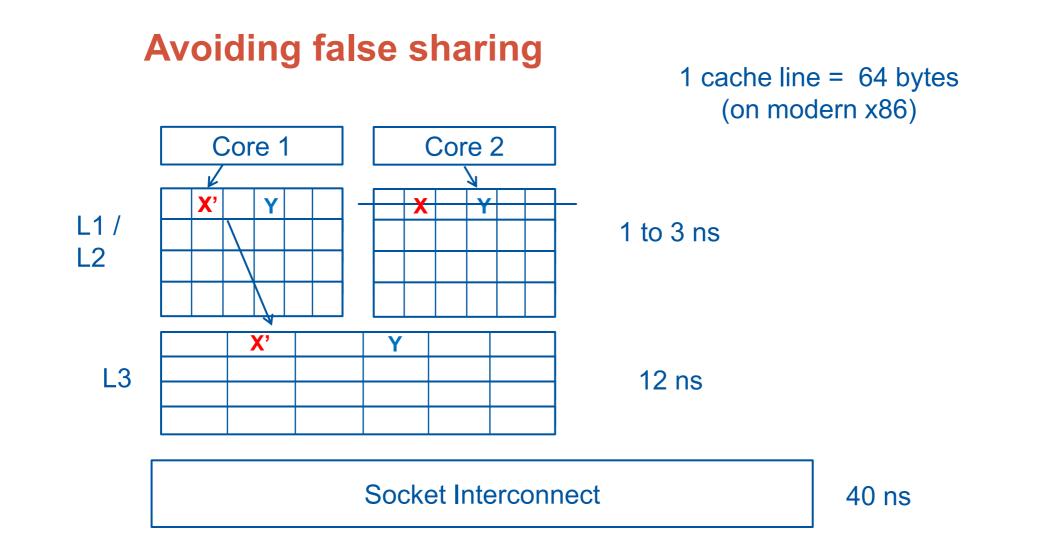

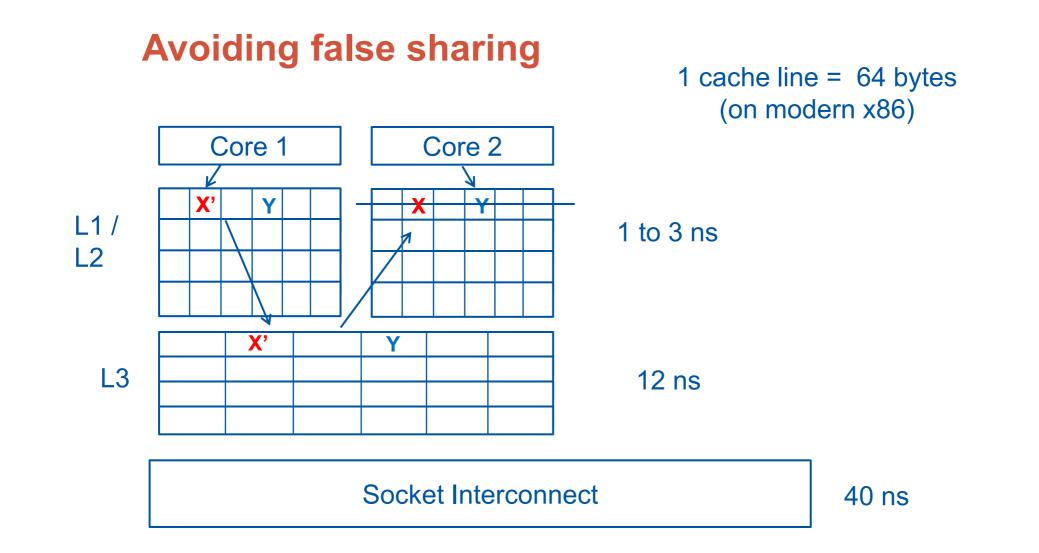

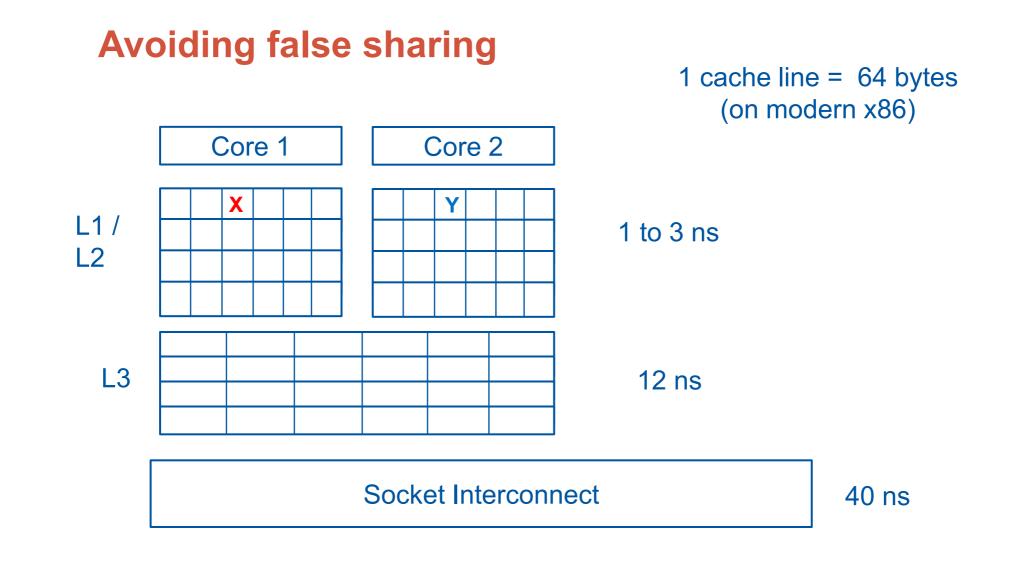

- The sequence number is a padded long  $\rightarrow$  no false sharing

- Represented internally as an array  $\rightarrow$  caches gets prefetched

- The sequence number is a padded long  $\rightarrow$  no false sharing

- The memory visibility relies on the volatile sequence number  $\rightarrow$  no locks

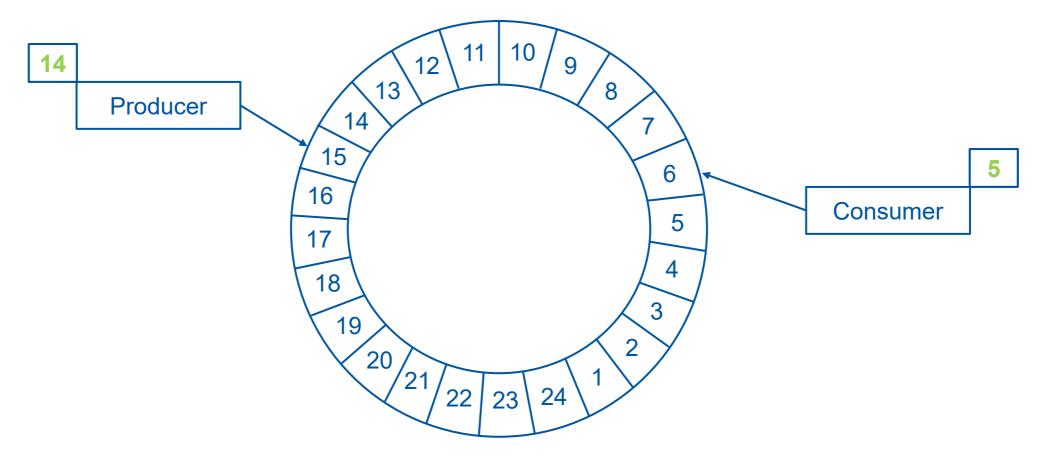

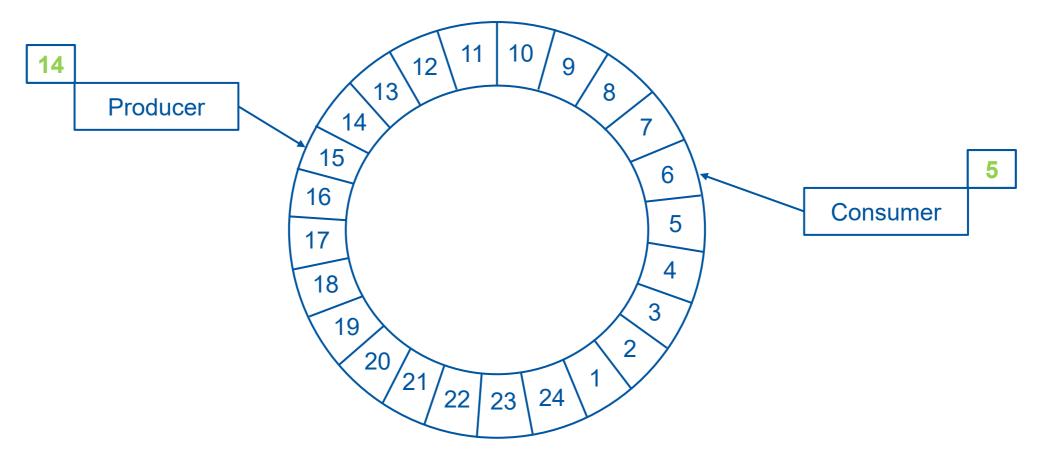

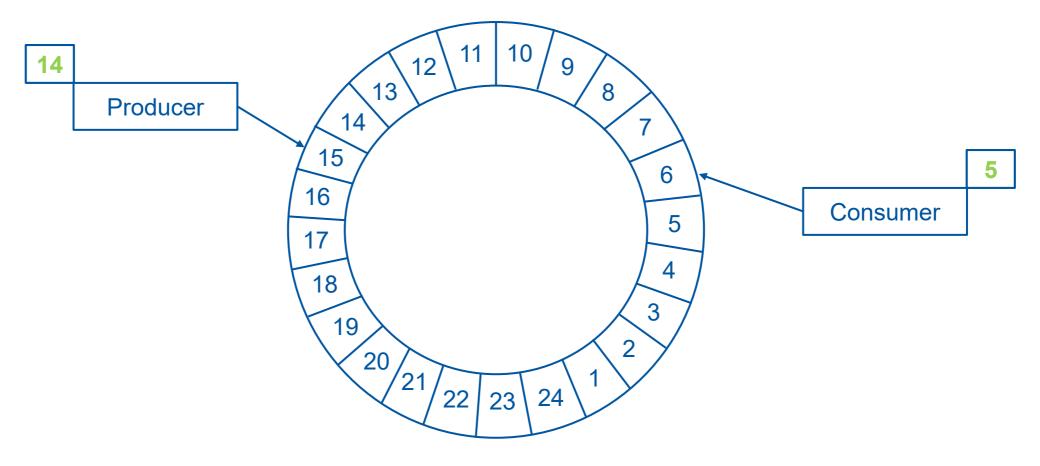

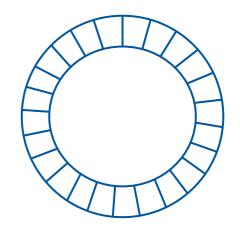

### The mighty ring buffer

- Represented internally as an array  $\rightarrow$  caches gets prefetched

- The sequence number is a padded long  $\rightarrow$  no false sharing

- The memory visibility relies on the volatile sequence number  $\rightarrow$  no locks

- Slots are preallocated  $\rightarrow$  no garbage collection

$\rightarrow$  Latency and jitter reduced to a minimum

- $\rightarrow$  Latency and jitter reduced to a minimum

- $\rightarrow$  No garbage collection

- → Latency and jitter reduced to a minimum

- $\rightarrow$  No garbage collection

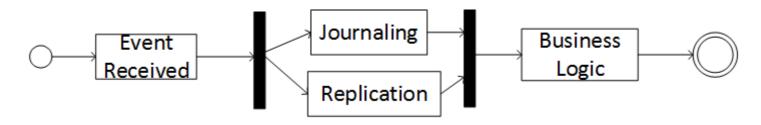

- → Can have multiple consumers organized in a graph of dependency

- → Latency and jitter reduced to a minimum

- $\rightarrow$  No garbage collection

- → Can have multiple consumers organized in a graph of dependency

→ Consumers can use batching to catch up with producers

#### → Performance

No locks, no garbage collection, CPU friendly

#### → Performance

No locks, no garbage collection, CPU friendly

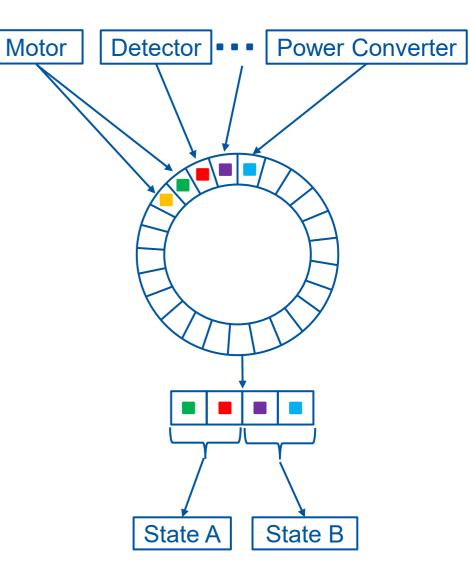

#### → Determinism

The order in which events were processed is known Messages can be replayed to rebuild the server state

#### → Performance

No locks, no garbage collection, CPU friendly

#### → Determinism

The order in which events were processed is known Messages can be replayed to rebuild the server state

#### $\rightarrow$ Simplification of the code base

Since the business logic runs on a single thread, there is no need to worry about concurrency

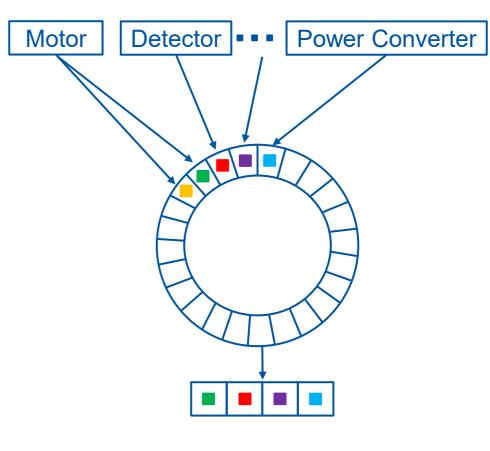

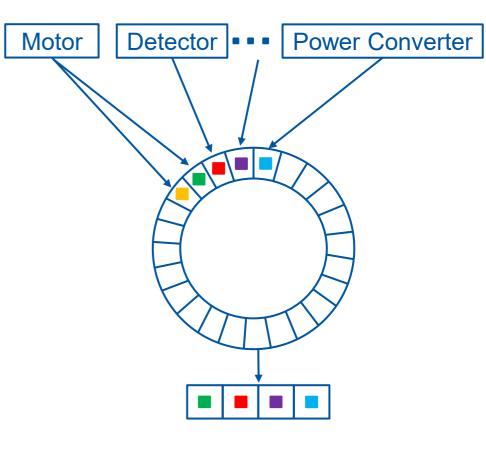

$\rightarrow$  Each event received from hardware is stored on the ring buffer

$\rightarrow$  Each event received from hardware is stored on the ring buffer

$\rightarrow$  For each stream of data, the last value is kept

$\rightarrow$  Each event received from hardware is stored on the ring buffer

$\rightarrow$  For each stream of data, the last value is kept

$\rightarrow$  We make use of batching

$\rightarrow$  Each event received from hardware is stored on the ring buffer

- $\rightarrow$  For each stream of data, the last value is kept

- $\rightarrow$  We make use of batching

- $\rightarrow$  At the end of a batch, the business logic is triggered and executed on a single thread

$\rightarrow$  Each event received from hardware is stored on the ring buffer

- $\rightarrow$  For each stream of data, the last value is kept

- $\rightarrow$  We make use of batching

- $\rightarrow$  At the end of a batch, the business logic is triggered and executed on a single thread

- $\rightarrow$  Publish the new states over the network, making sure that we do not block the Disruptor thread if the message broker is down

## Conclusions

- The Disruptor, a tool from the world of finance, fits really well in an Accelerator control system

- It simplified the CERN CESAR code base while handling the flow of data more efficiently

- It is easily integrated in an existing design to replace a queue or a full pipeline of queues

- The main challenge faced was to switch the developers' mind-set to think in asynchronous terms

## **Useful Links**

• The Disruptor main page with an introduction and code samples: http://lmax-exchange.github.io/disruptor

Presentation of the Disruptor at Qcon

<a href="http://www.infoq.com/presentations/LMAX">http://www.infoq.com/presentations/LMAX</a>

An article from Martin Fowler:

<a href="http://martinfowler.com/articles/lmax.html">http://martinfowler.com/articles/lmax.html</a>

• A useful presentation on Latency by Gil Tene who shows that most of what we measure during performance test is wrong:

http://www.infoq.com/presentations/latency-pitfalls

• New Async logger in Log4J 2

http://logging.apache.org/log4j/2.x/manual/async.html

www.cern.ch