Tomasz Włostowski

Beams Department Controls Group Hardware and Timing Section

# Developing hard real-time systems using FPGAs and soft CPU cores

Melbourne, 22 October 2015

### Outline

- Hard Real Time control systems: background

- The Mock Turtle Core

- The  $\mu RV$  a soft processor core designed at CERN

- Application examples

- Summary and outlook

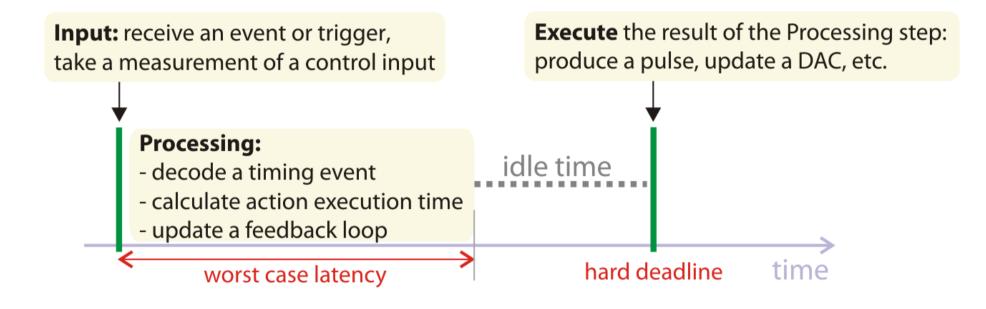

### Hard Real Time Controls What do we mean by hard RT?

## Hard RT: technologies

#### **FPGAs**

| <ul> <li>Very low and deterministic latency</li> <li>Easy to customize</li> <li>Long development cycle</li> <li>Difficult to program by the end user</li> </ul> | <ul> <li>Deterministic latency</li> <li>Easy to program</li> <li>Difficult to customize (often need a companion FPGA)</li> <li>Portability issues</li> </ul>                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLCs                                                                                                                                                            | Linux PCs                                                                                                                                                                               |

| <ul> <li>Standardized environment</li> <li>Easy to program by the end users</li> <li>Too slow for many accelerator applications</li> </ul>                      | <ul> <li>Very short development cycle</li> <li>Easy to program by the end users</li> <li>Can't guarantee determinism         <ul> <li>(at least on x86 platform)</li> </ul> </li> </ul> |

T. Włostowski Developing hard real-time systems using FPGAs and soft CPU cores

**Embedded processors**

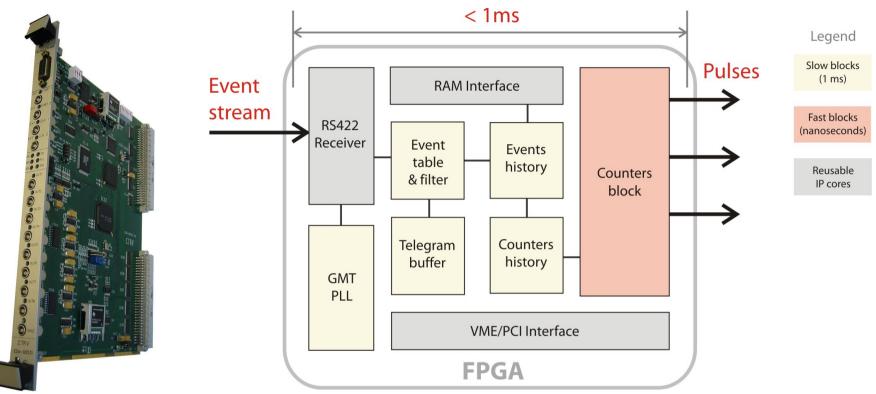

### Example: CERN timing receiver

- Custom VHDL design, done from scratch

- Only a small part (counters) really needs dedicated VHDL

- Limited flexibility

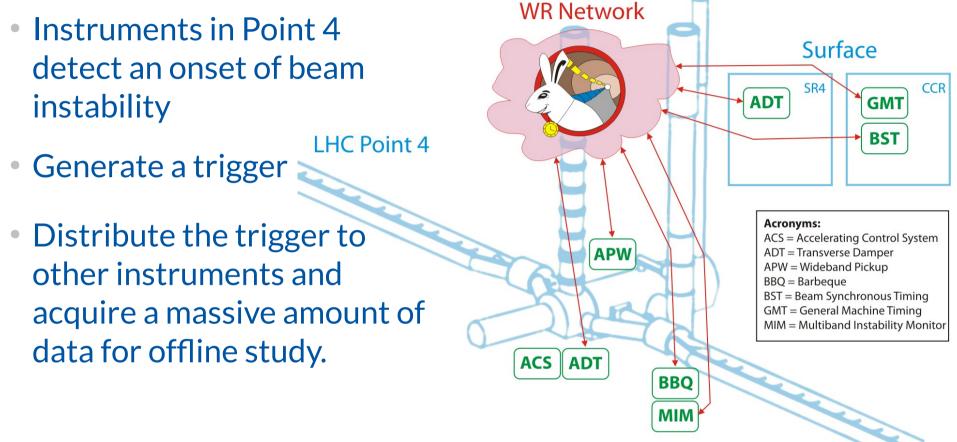

### Example: LHC Instability Trigger a.k.a. The LIST

T. Włostowski Developing hard real-time systems using FPGAs and soft CPU cores

6

### LIST: The Challenge

#### **Distributed hard real time system**

- Exchange triggers between any pair of devices in the network

- Never exceed the design latency (max 270 µs)

- Never miss a trigger

- Deliver a feature-rich system in a reasonable time...

T. Włostowski Developing hard real-time systems using FPGAs and soft CPU cores

7

## Hard RT: technologies

#### **FPGAs**

Deterministic latency Very low and deterministic latency Easy to program Easy to customize × Difficult to customize (often need a **x** Long development cycle companion FPGA) **×** Difficult to program by the end user **×** Portability issues **PLCs Linux PCs**  Standardized environment Very short development cycle Easy to program by the end users Easy to program by the end users **x** Too slow for many accelerator × Can't guarantee determinism applications (at least on x86 platform)

T. Włostowski Developing hard real-time systems using FPGAs and soft CPU cores

**Embedded processors**

### Outline

- Hard Real Time control systems: background

- The Mock Turtle Core

- The  $\mu RV$  a soft processor core designed at CERN

- Application examples

- Summary and outlook

T. Włostowski Developing hard real-time systems using FPGAs and soft CPU cores

9

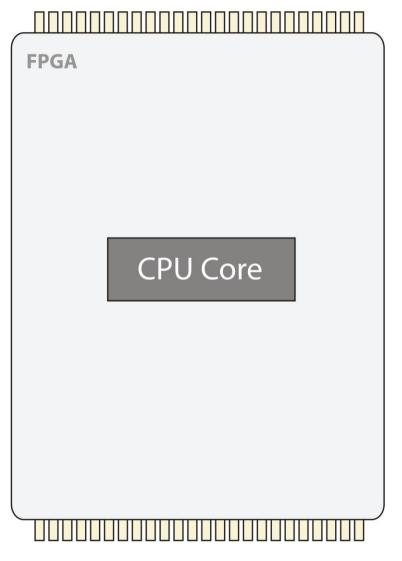

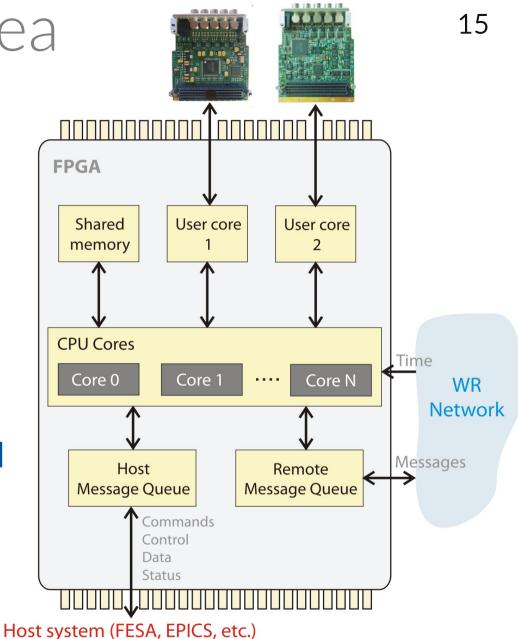

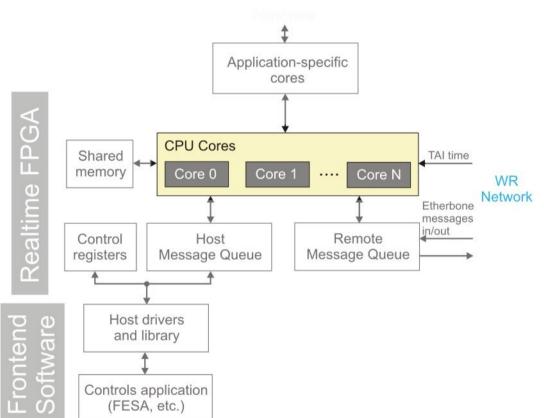

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

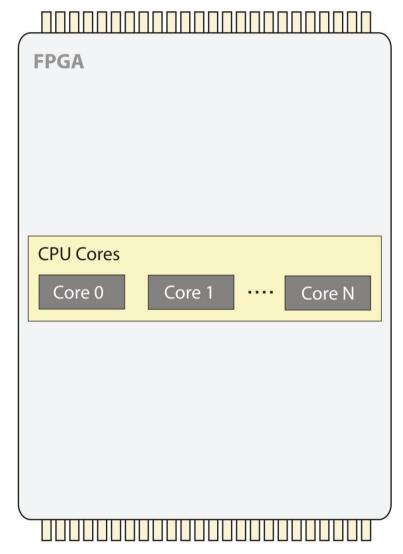

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

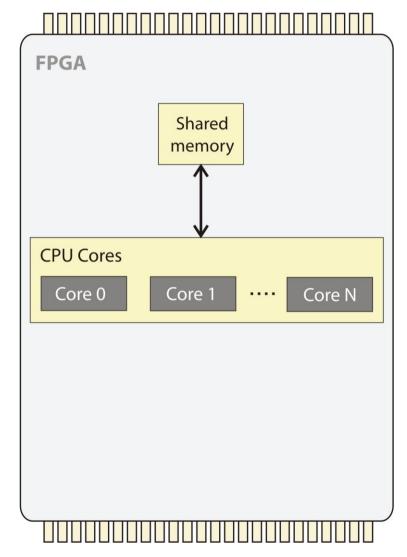

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

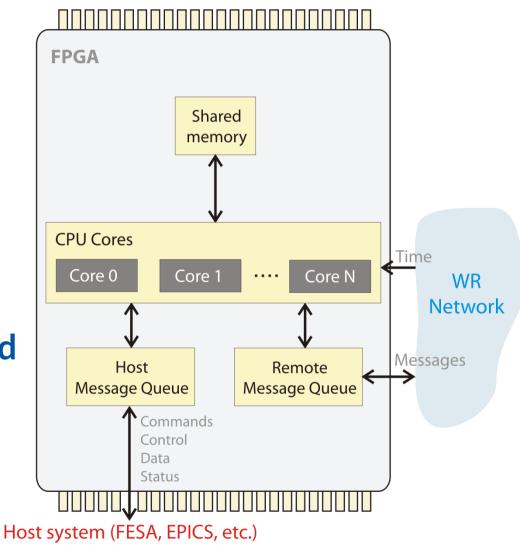

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

- Take an FPGA chip

- Take a CPU core that is deterministic

- Put as many CPUs as needed

- Let them communicate with each other...

- ... and with the external world

- Connect user cores and hardware

User hardware

### Make it a service!

- Standard.

- Portable.

- Reusable.

- With or without White Rabbit as the means of communication and synchronization.

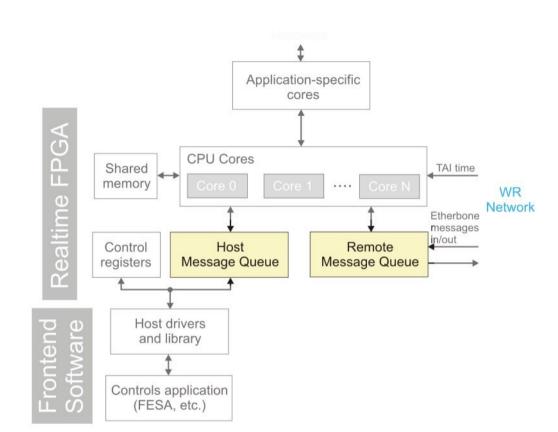

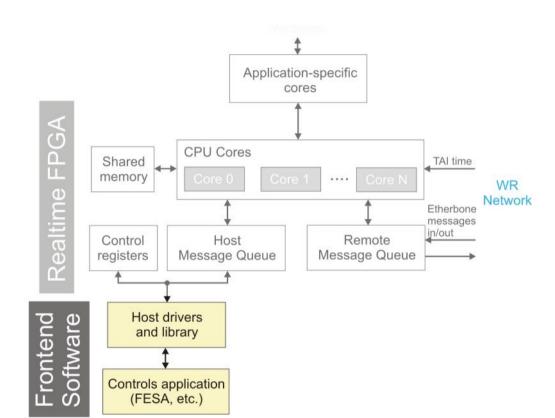

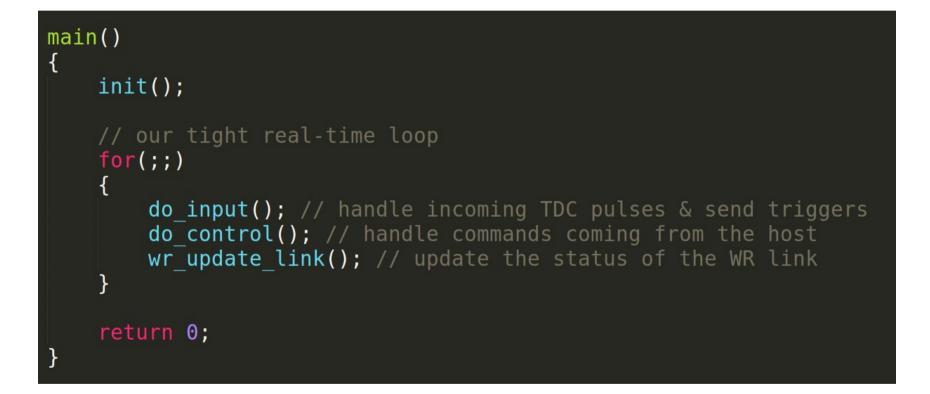

### Inside Mock Turtle The CPU Cores

- Up to 8 LM32 cores, with private code/data memory

- Programed in bare metal C, using standard GCC tool chain

- Each core runs a single task in a tight loop.

- No caches, no interrupts

- Program loading and flow control from the host system

- Run with same time base if used with WR

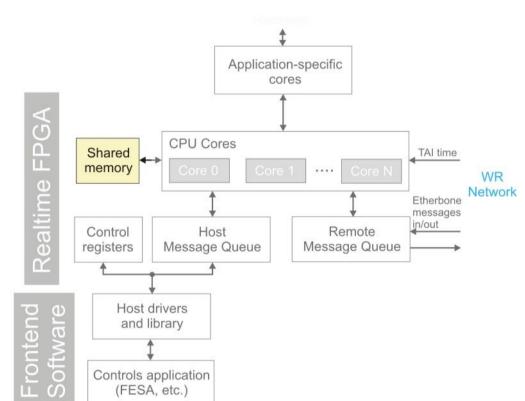

### Inside Mock Turtle Shared Memory

- Foreseen for inter-core communication and task synchronization

- Small, but atomically accessed

- Add/subtract

- Bit operations

- Test-and-set

- Task synchronization primitives

- Mutexes

- Semaphores

- Queues

- Flags

- Events...

# Inside Mock Turtle

#### **Communication System**

- Simple FIFO queues holding multiple messages

- Polling in a tight loop on the RT side

- Interrupt-driven on the host side

- Each queue provides a configurable number of channels (slots)

- Host Message Queue for communication with the host software

- Optional Remote Message Queue for communication with other nodes over WR network

- Uses Etherbone protocol

#### Inside Mock Turtle Software Architecture

- Unified kernel driver + user space C library

- Host code written in user space

→ easier development

- Message Queue and Shared Memory access

- Loading CPU applications and controlling each core's execution flow

- Real-time library for the CPU cores.

- Python bindings available.

20

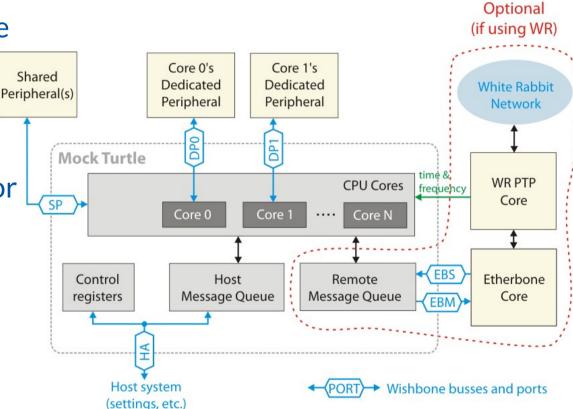

### Outside Mock Turtle

Interfaces & integration in user design

- Based on the Wishbone bus.

- Each CPU can have its exclusive Dedicated Peripheral.

- All CPUs can access Shared Peripheral(s).

- Etherbone master/slave port for communication with other nodes in a WR network (optional).

- Time interface from the WR PTP Core.

- Control port for the host system.

### Outline

- Hard Real Time control systems: background

- The Mock Turtle Core

- The  $\mu RV$  a soft processor core designed at CERN

- Application examples

- Summary and outlook

# What is **µRV**?

- Micro RISC-V: a compact soft processor (CPU) core for use in FPGAs.

- $\rightarrow$  Written in Verilog, no external dependencies.

- Reduced Instruction Set (RISC) processor.

- → Small number of instructions, each doing one function at a time.

- Based on the RISC-V architecture developed at the University of Berkeley.

- $\rightarrow$  Well thought and promising instruction set.

- Small, portable and deterministic.

- $\rightarrow$  Determinism of execution over performance.

# Why $\mu RV$ ?

- A number of our projects depend on soft CPUs

- Popular architectures have either license limitations (LM32) or are patented (ARM, MIPS)

- FPGA vendor-provided cores (Microblaze, Nios) are not portable (no sources available either)

- RISC-V: a very nice architecture, but with no small Verilog/VHDL implementation

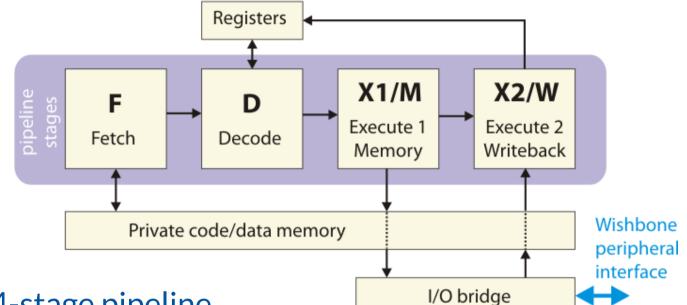

# The **µRV** design

- Simple, 4-stage pipeline

- All instructions except jumps (branches) in one clock cycle

- Code/data in a private memory

- Wishbone bus for peripheral access

- 100 MHz and 20% of a small FPGA (Spartan-6 SLX9)

### Outline

- Hard Real Time control systems: background

- The Mock Turtle Core

- The  $\mu RV$  a soft processor core designed at CERN

- Application examples

- Summary and outlook

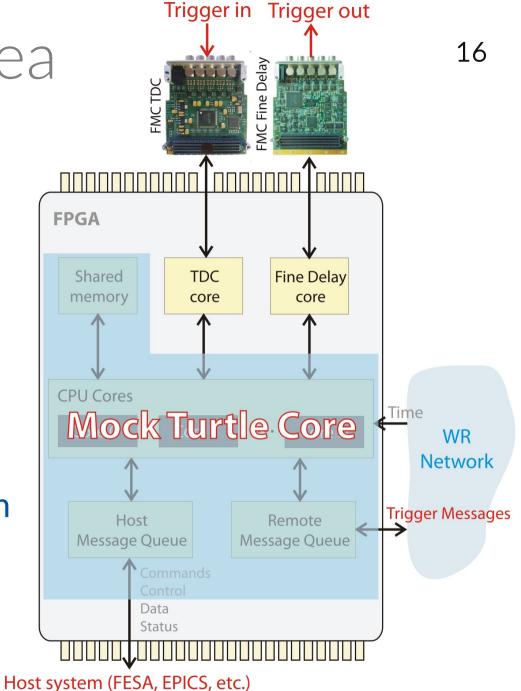

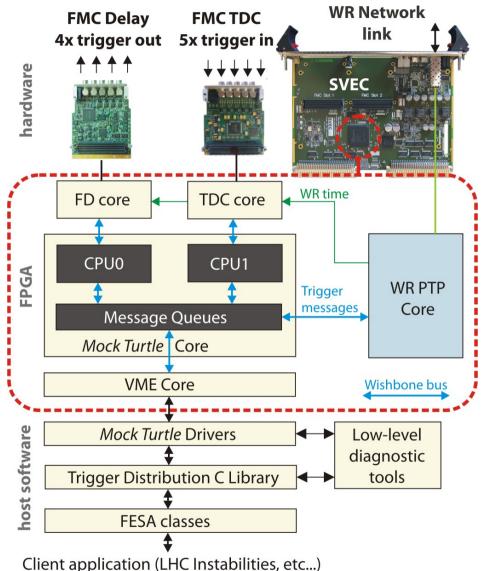

## Trigger Distribution Node

- Dual-core system:

- 32 kB private RAM per CPU

- CPU 1 responsible for the inputs:

- Poll TDC for incoming pulses

- Apply dead time

- Assign trigger ID

- Send to the WR network

- Log the trigger

- CPU 0 takes care of the outputs:

- Poll Remote MQ for trigger messages

- Search a hash table for matching triggers

- Apply delay & dead time

- Program the pulse generator

- Log the trigger

### Trigger Distribution Node Example of a real time task

### Outline

- Hard Real Time control systems: background

- The Mock Turtle Core

- The  $\mu RV$  a soft processor core designed at CERN

- Application examples

- Summary and outlook

### Summary & outlook

- Proven real-time performance

- Trigger distribution system working in the LHC

- Other projects (FIP master & RF distribution) ongoing

- Savings in development time

- Minimal amount of dedicated VHDL

- Standardized software stack and interfaces

- A service that anyone can use

- The µRV soft processor

- Passes CoreMark & official RISC-V test suite

- Migration of MT Cores from LM32 in progress

#### Sources available

at the Open Hardware Repository: ohwr.org

### Questions?

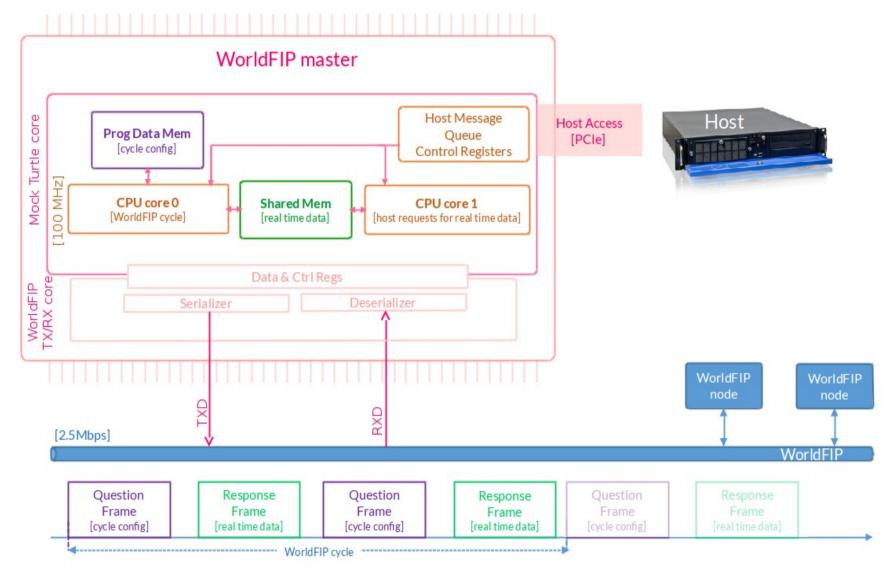

### MasterFIP project

### MasterFIP project

- Clean implementation of WorldFIP bus master

- Critical technology for LHC controls in radiation areas

- Two-CPU design

- CPU0 plays the current FIP macrocycle

- CPU1 exchanges the cycle configuration and variables with the host

- Dedicated VHDL only needed to serialize/deserialize FIP frames

- Shared Memory holds the FIP variables and macrocycle setup

- No White Rabbit