## THE POWER SUPPLY CONTROL SYSTEM OF CSR\* W. Zhang, S.An, S.Z.Gou, K.W.Gu, Y.P.Wang , P. Li, M.Yue IMP, LAN Zhou 730000, P.R. China

This article gives a brief description of the power supply control system for Cooler Storage Ring (CSR). It introduces in detail mainly of the control system architecture, hardware and software. We use standard distributed control system (DCS) architecture. The software is the standard three-layer structure. OPI layer realizes data generation and monitoring. The intermediate layer is a data processing and transmission. Device control layer performs data output of the power supply. We use ARM + DSP controller designed by ourselves for controlling the power supply output. At the same time, we have adopted the FPGA controller designed for timing for power supply control in order to meet the requirements of accelerator synchronizes the output of the power supply.

## INTRODUCTION

CSR is a double ring system. In every operation cycle, the stable-nucleus beams from the injectors are accumulated, cooled and accelerated in the main ring (CSRm), then extracted fast to produce RIB or highly charged ions. The experimental ring (CSRe) can obtain the secondary beams once for every operation cycle. The accumulation duration of CSRm is about 10 s. considering the ramping rate of magnetic field in the dipole magnets to be 0.1–0.4 T/s, the acceleration time of CSRm will be nearly 3 s. Thus, the operation cycle is about 17 s [2]. In CSRe, two operation modes will be adopted. One is the storage mode used for internaltarget experiments or high-precision spectroscopy with electron cooling. Another one is the deceleration-storage mode used for atomic-physics experiments.

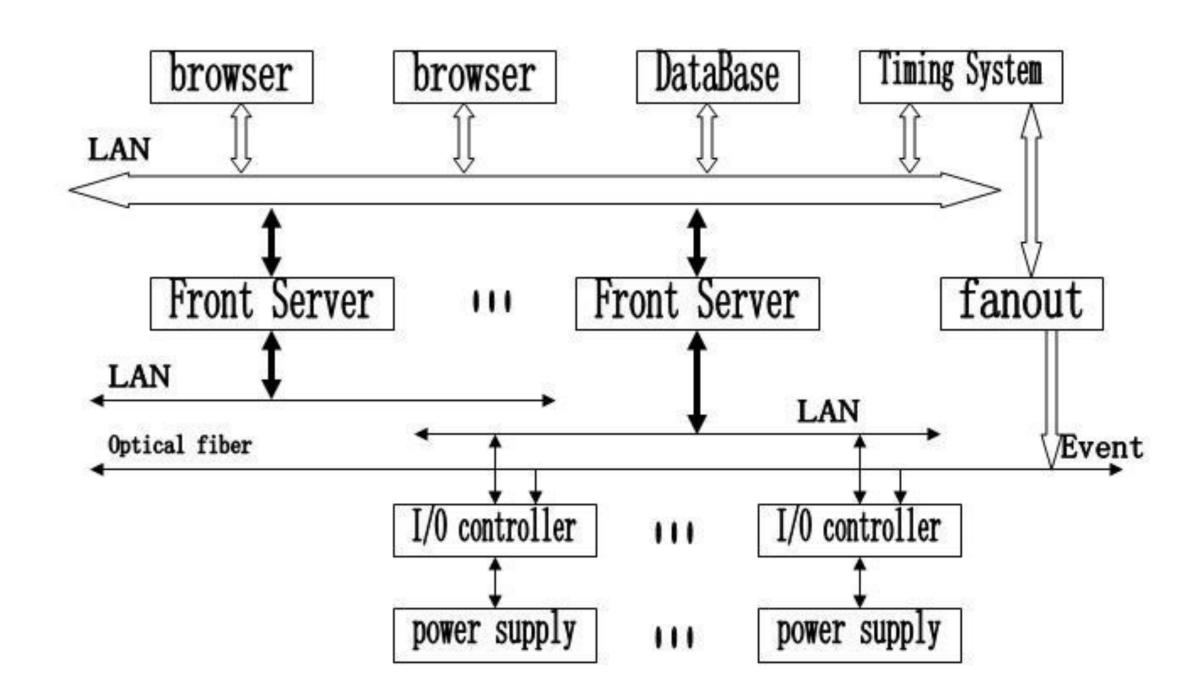

The control system is based on the Ethernet star topology. It takes Ethernet as the transmission medium to connect each part, mainly including: database system, the synchronization server, the front end server, the I/O part (ARM controller and the DSP processor) and the communication module. Database system and synchronization server is the information and control centre of the whole system. There is an independent Ethernet connection between the front end of the server and the I/O component, and a front-end server manages multiple I/O components. The I/O part directly controls the device object, and an I/O part controls one or four device objects. The structure of the power control system is shown in Figure 1. In the system, power control is accomplished by three kinds of data files: process data, event table data and command table data. In the power supply control system, the ARM controller is directly used as a network node to realize the information exchange between the upper control centres; at the same time, the DSP control board is used as the control unit, and the real-time and accurate monitoring of the control equipment is carried out.

## Fig1: The structure of the power control system

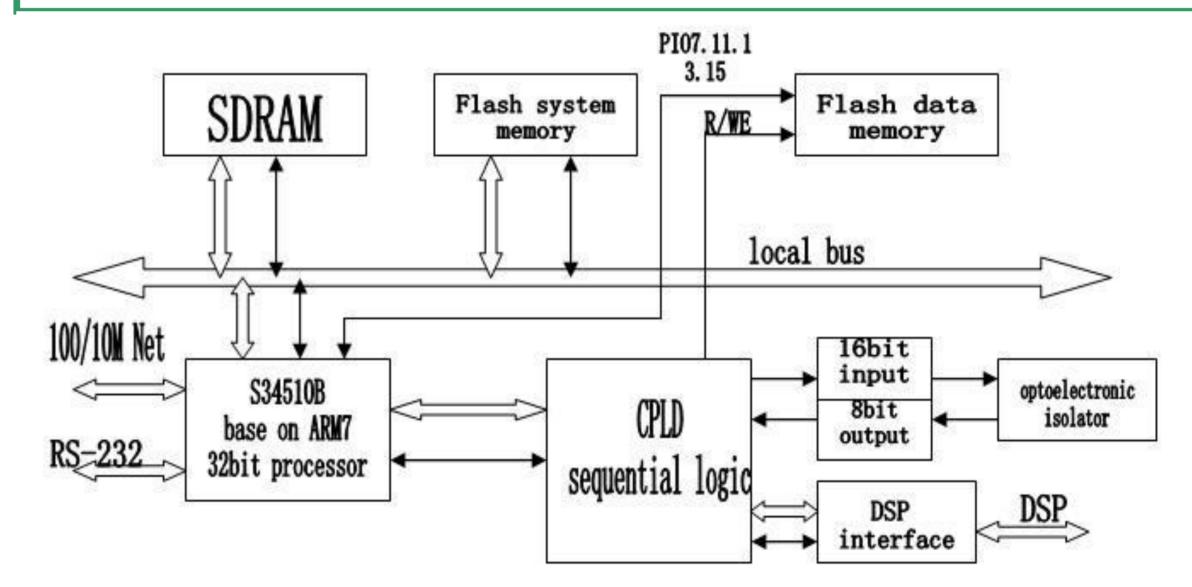

The ARM controller with S3C4510B as the core, connects DSP through the back, and is provided by a power supply for the backing plate. The structure of the ARM controller is shown in Figure 2.ARM controller with SDRAM, Flash, data CPLD and system Flash. It receives data files (process data, event data, and command table) data) through the network; Data transmission to the DSP through the HPI port of DSP; System Flash for curing uboot, kernel and root file system; Data Flash is used to store the important control parameters and waveform data, so as to avoid the loss of data.

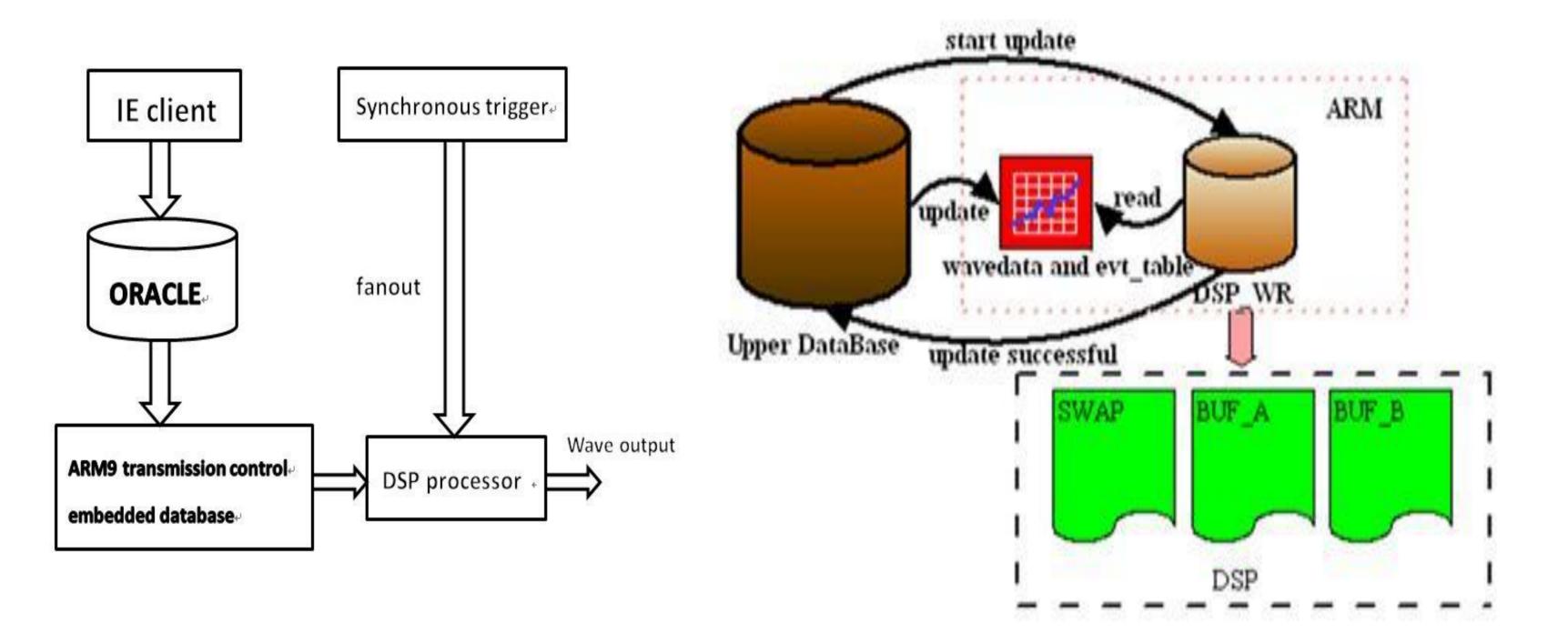

The power supply control system uses the C/S structure. The structure of the software is shown in Figure 4. The first layer is a synchronization server. It is through the data exchange with the database system to get the accelerator's effective operation data and distribution, and also provides the time system of the trigger event and customer operation procedures. Database service is second layer. It provides the synchronization data file required by the CSR to run an independent cycle. A network connection is used between the synchronous server and the I/O component and the database system.

Fig 2: The structure of the ARM controller.

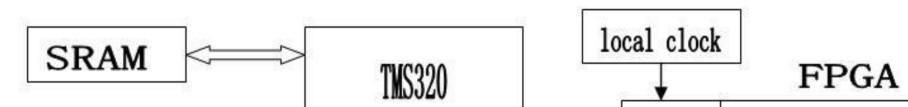

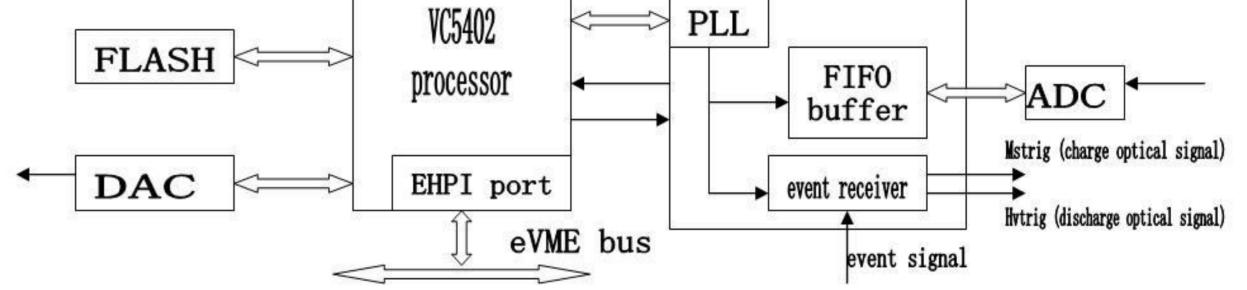

The DSP processor is connected to the ARM controller by the backing board, and the power supply is provided by the backing plate. The structure of the DSP processor is shown in Figure 3.It takes TMS320VC5402 as the core, and the SRAM and Flash of 512K\*16bit. Through the back board, the DSP processor receives the process data and event data from the HPI port of the ARM controller, and stores it in the SRAM. The trigger event is received by the FPGA case of a light switch. Flash used to cure DSP programs and procedures. The DSP processor has a DAC and an ADC channel.

## Fig4: The structure of the software Fig 5 The waveform data download flow chart

We provide a web interface program based on Web technology, which can be easily loaded into the Oracle database in the front end of the binary waveform file. The waveform data is passed to the database file of the front controller by update command and the IP address of the initial set of the front-end controller, at the same time to inform the embedded database SQLite has a new data to arrive. The embedded database stores the new data according to the distribution of the DSP storage space and the current waveform output buffer. When the required data is passed to the DSP storage space, we can start the pulse trigger program to generate the optical pulse signal. After the trigger event is consistent, the DSP processor outputs the waveform. The waveform data download flow chart is shown in Figure 5.

Fig 3: The structure of the DSP processor.

The control system has been applied to the actual operation in 2008 and passed the acceptance of the CSR expert group. It implements the requirements of the power supply control system for the CSR project. The control system has been stable operation of the seven-and-a-half years, and ensures the normal conduct of the experiment.

Institute of Modern Physics, Chinese Academy of Sciences