# PANDA MOTION PROJECT - A COLLABORATION BETWEEN SOLEIL AND DIAMOND TO UPGRADE THEIR 'POSITION AND ACQUISITION' PROCESSING PLATFORM

I.S. Uzun, T. Cobb, A. Cousins, M.T. Heron Diamond Light Source, Oxfordshire, UK Y.M. Abiven, J. Bisou, P. Monteiro, G. Renaud SOLEIL, Gif-sur-Yvette, France

#### Collaboration

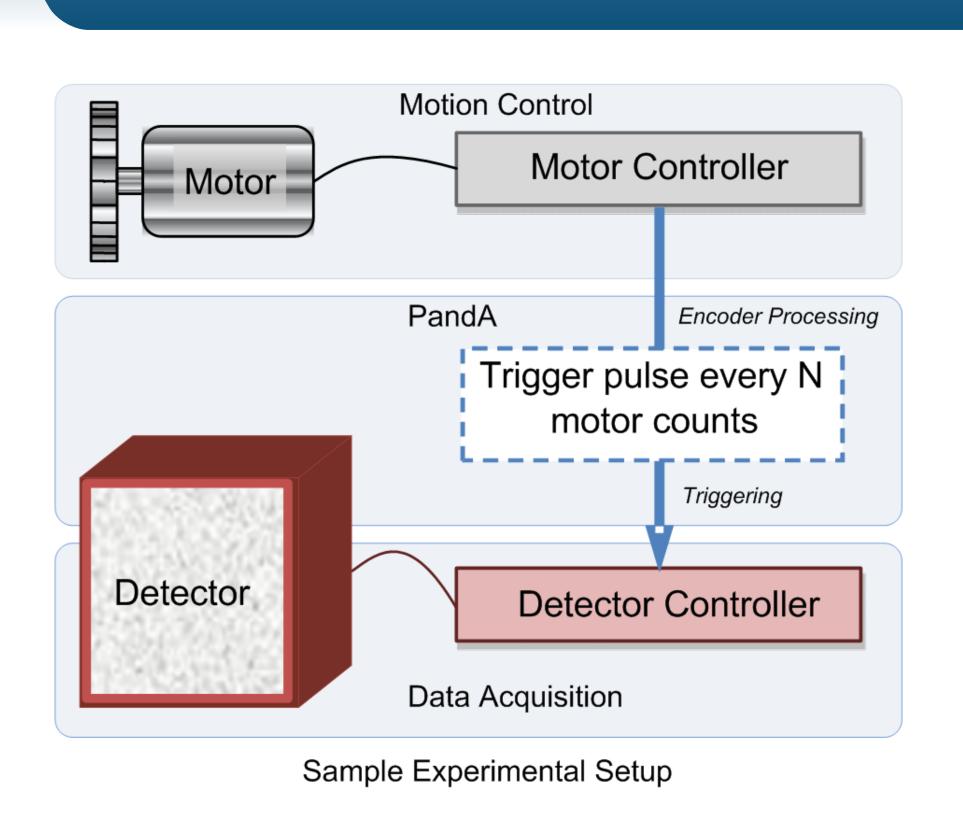

PandA will provide a common synchronous triggering and data capture platform for simultaneous and multi-technique scanning applications with support of multiple encoder standards.

- Both institutes want to standardize hardware, in order to reduce number of systems which need to be developed and maintained by the support staff.

- Develop a ready to use and complete solution, in order to install quickly and easily all the hardware and software components.

It will provide a flexible and open solution to interface different third party hardware (detectors and motion Controllers).

| Task leadership          | DIAMOND | SOLEIL |

|--------------------------|---------|--------|

| Project management       | X       |        |

| HW, FW specifications    | X       | X      |

| Schematic Design         |         | X      |

| PCB Layout               |         | X      |

| Mechanics                |         | X      |

| FPGA – Zynq Processor    |         |        |

| Design                   | X       |        |

| FPGA – Zynq Logic        |         |        |

| Design                   | X       |        |

| Linux Kernel Development | X       |        |

| Linux Application        |         |        |

| Development              | X       |        |

| TANGO interface          |         | X      |

| EPICS interface          | X       |        |

Table 1: Task sharing between project partners.

### Hardware Architecture

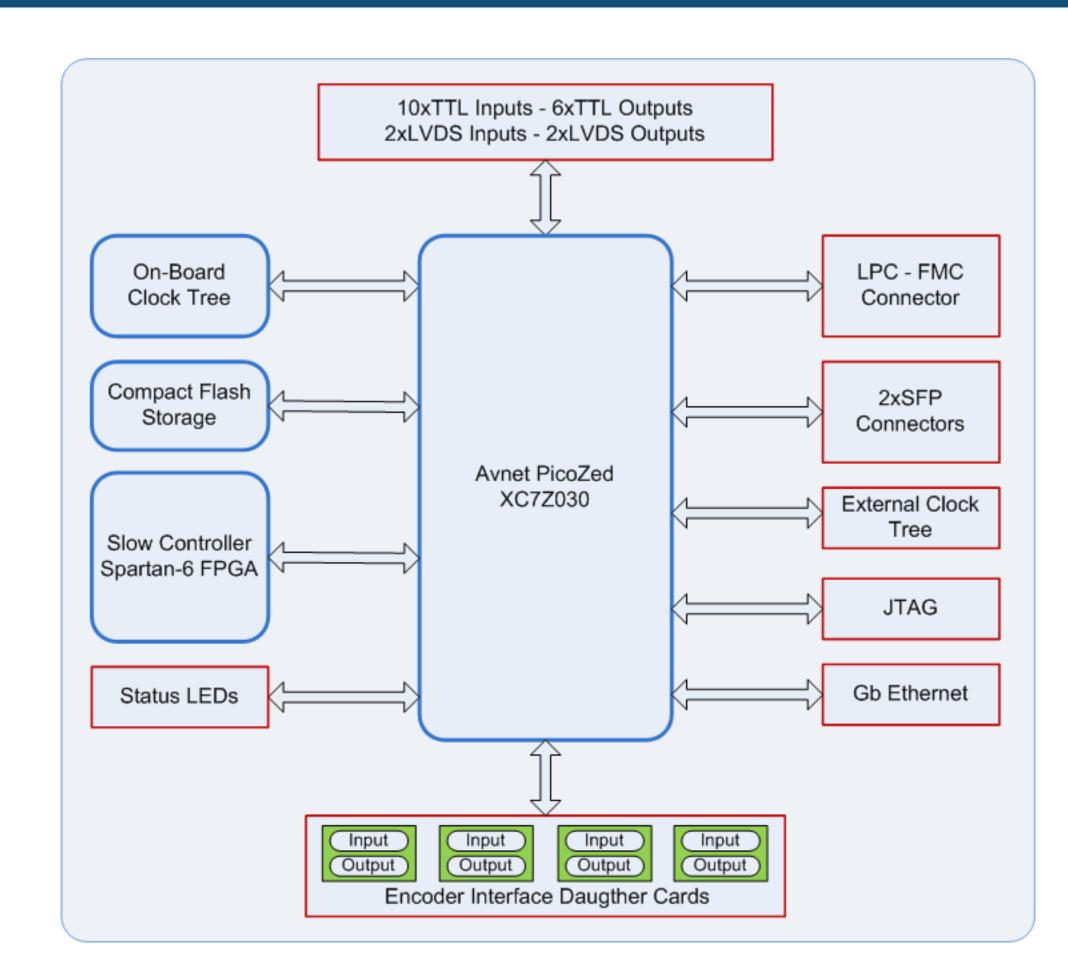

- Supports multi-channel TTL and LVDS I/O.

- Wide range of encoder standards (Incremental, SSI, EnDat and BisSS) via RS485.

- A fully compliant Low-Pin Count FMC slot.

- 3-Channels of SFP Gigabit Transceiver interface.

- Gigabit ethernet connectivity.

# Firmware Design

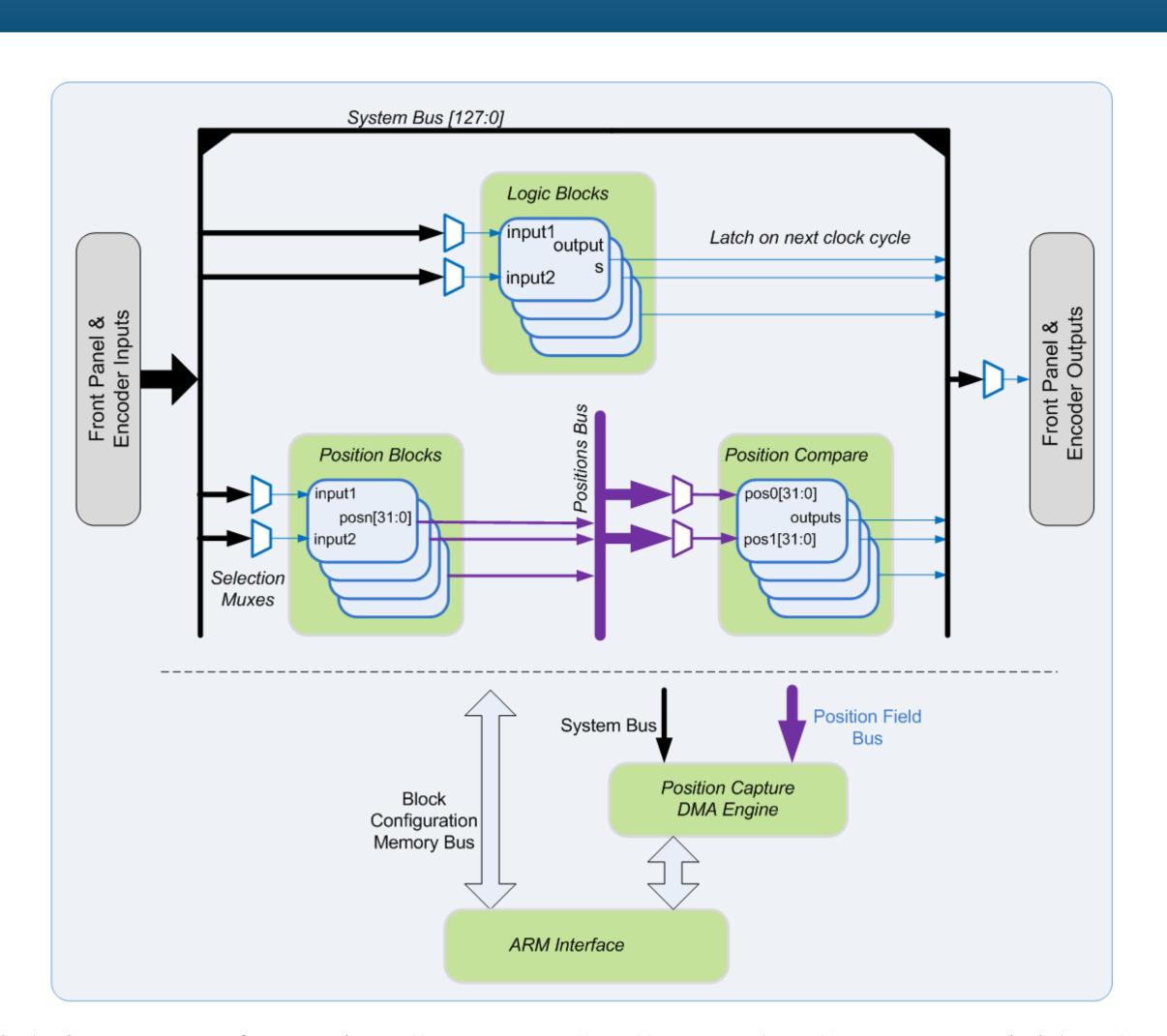

- Multiple instances of Function Generator, SR Gate, Pulse Generator, Divider, Sequencer and Clock Generator blocks.

- Multiple instances of Encoder Input and Output, Quadrature Input and Output, Counter/Timer and Analog I/O (via FMC) blocks.

- Multiple Position Compare and Capture blocks.

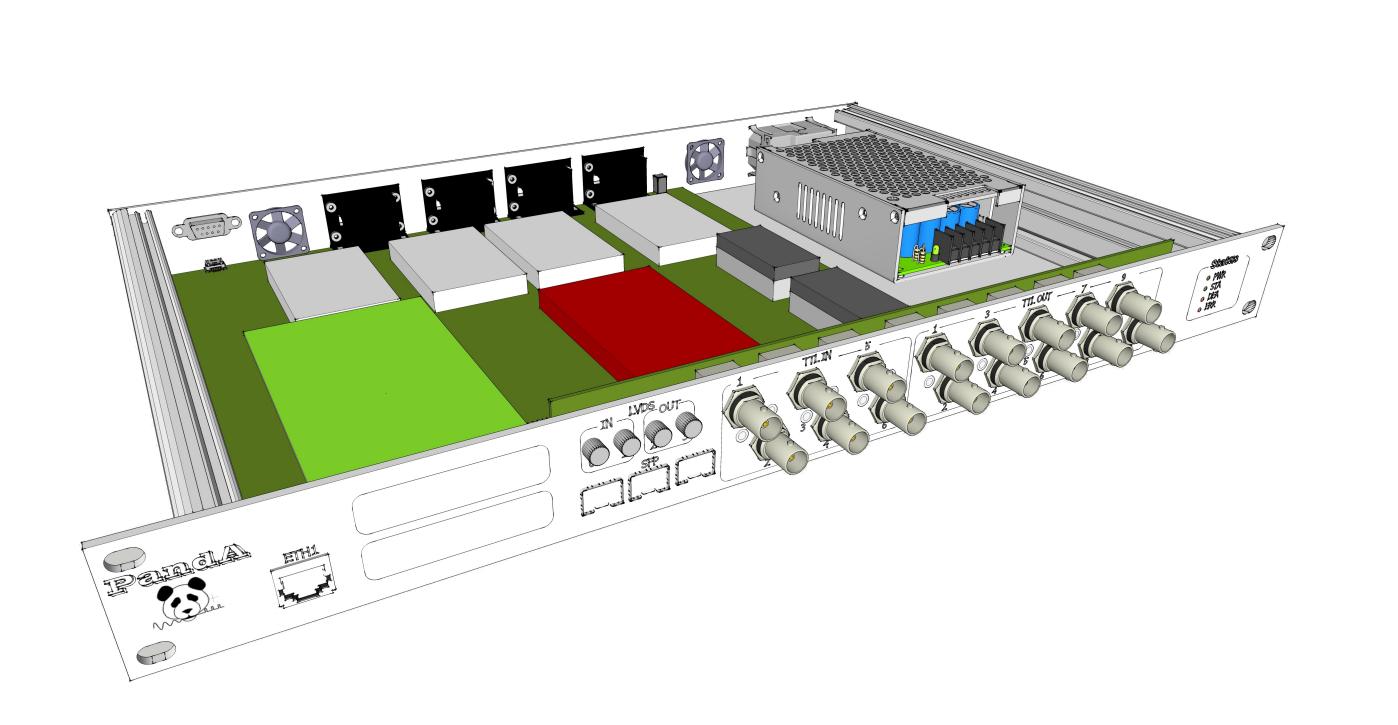

## Mechanics

PandA will consists of a 1U metal box, with BNC and LEMO connectors for single ended, differential signals and Gigabit Ethernet on the front panel. 15-way D-type connectors for RS485 encoder signals and power on the back panel.

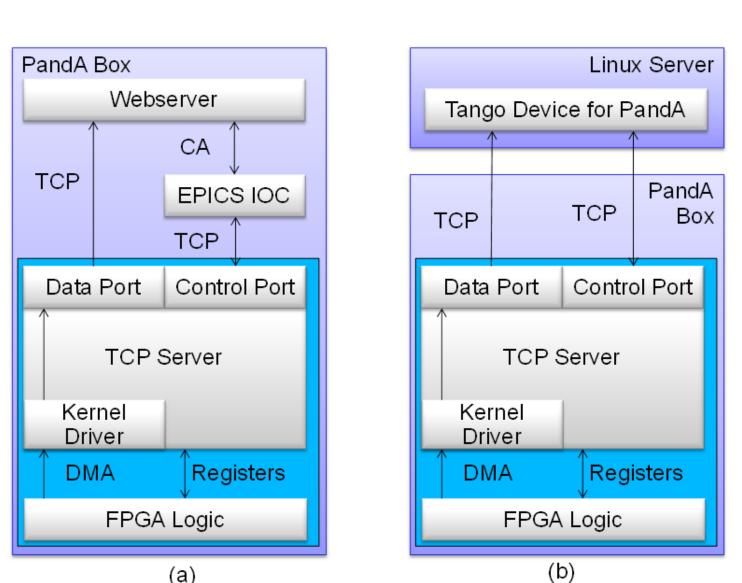

# Software Architecture

The Zynq-Arm will run linux and use a dedicated linux device to tightly integrate with the FPGA logic.

Common Layers:

- Kernel driver.

- TCP Server for data and control.

PandA will be integrated either with an EPICS IOC, a webserver interface, or with a separate TANGO server.