# The AccTesting framework: an extensible framework for accelerator **commissioning and systematic testing** D. Anderson, M. Audrain, K. Fuchsberger, J.C. Garnier, R. Gorbonosov, A.A. Gorzawski, A. Jalal,

A. Moscatelli, P.C. Turcu, K. Stamos, M. Zerlauth (CERN, Geneva, Switzerland)

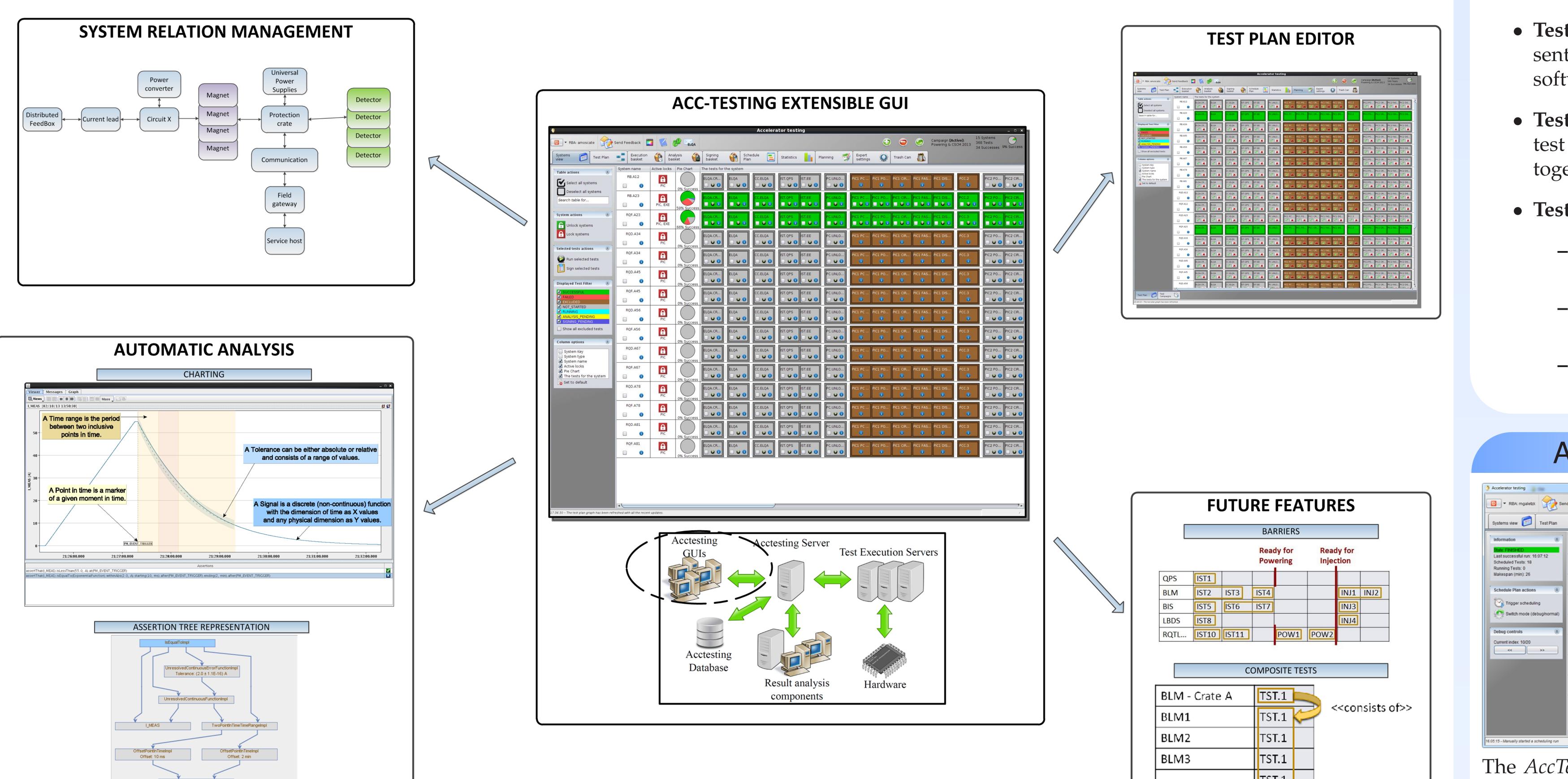

The Large Hadron Collider (LHC) at CERN requires many systems to work closely together to allow reliable operation and at the same time ensure the correct functioning of the protection systems required when operating with large energies stored in magnet systems and particle beams. The systems for magnet powering and beam operation are qualified during dedicated commissioning periods and retested after corrective or regular maintenance. Based on the experience acquired with the initial commissioning campaigns of the LHC magnet powering system, a framework was developed to orchestrate the thousands of tests for electrical circuits and other systems of the LHC. The framework was carefully designed to be extendable. Currently, work is on-going to prepare and extend the framework for the re-commissioning of the machine protection systems at the end of 2014 after the LHC Long Shutdown. This paper describes the concept, current functionality and vision of this framework to cope with the required dependability of test execution and analysis.

# Abstract

### Overview

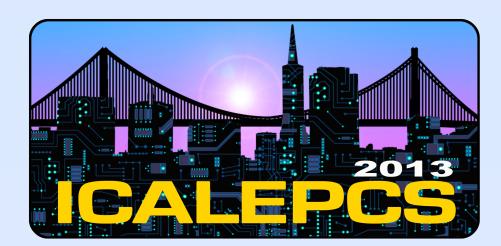

TestPhases: Depend on each other.

SystemTests: Per System

TestSteps:

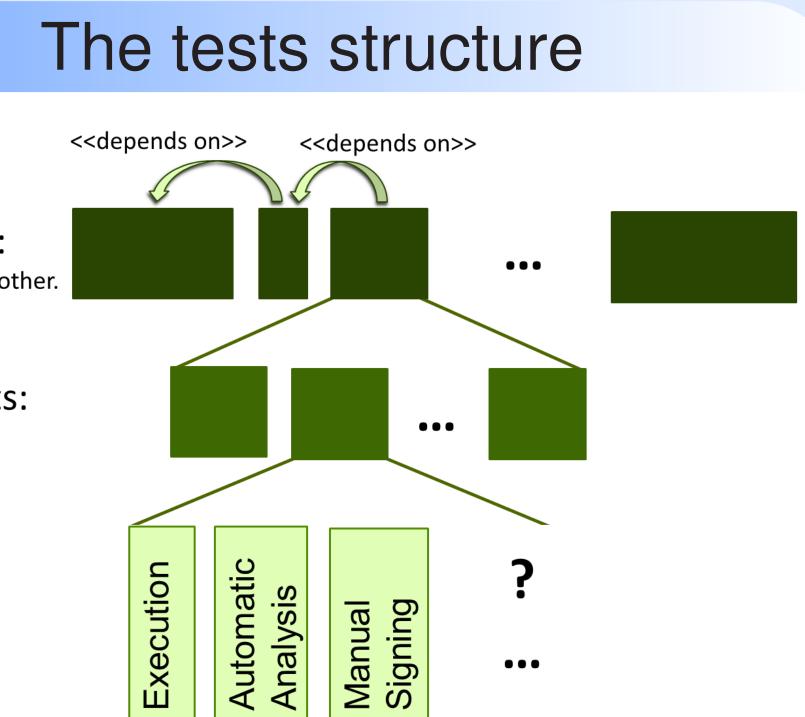

The AccTesting server plays a fondamental role in the framework, managing the schedule of all the tests required by all the users in parallel, ensuring the proper order of the steps and avoiding priority errors between them.

• **Tests:** The core block is a test which represents certain actions taken by hardware or software.

• Test phases: Each test belongs to exactly one test phase. The test phases group the tests together and depend on each other.

• **Test steps:** Each test has three test steps:

- *Execution*: the moment where something is actually done on the device.

- Analysis: the analysis of the results (the signals of the monitored system).

- *Signing*: some tests need the validation of one or more experts.

|                                     |         |                  |          | 1.1                | - |                     |                 |             |                 |                                  |

|-------------------------------------|---------|------------------|----------|--------------------|---|---------------------|-----------------|-------------|-----------------|----------------------------------|

| Fei                                 | odback  |                  | 0        | <u>s</u>           |   |                     |                 |             | 27              | STests O<br>Successes 6% Success |

| -                                   | B<br>bi | ecution<br>asket | <b>e</b> | Analysis<br>basket |   | Signing basket 🗌    | Schedule Plan 📃 | Statistics  | Expert settings | Trash Can                        |

| 2000F AV                            | (       | PIC2 QPS         | -ОК      |                    |   | D                   |                 |             |                 |                                  |

| ROTD A1                             | 8н.     | PCL              |          |                    |   | PCC.5               |                 |             |                 |                                  |

| 2009 A70                            |         | PLI1.b2          |          |                    |   | PLI1.d2             |                 |             |                 | PU2.62                           |

| RCSAL2828CDA1382CDA138R0TDA(2823A78 |         |                  |          |                    |   | PCL                 |                 | PCC.5       |                 | PIC2 CRY0-0K                     |

| RECOA13                             |         |                  |          |                    |   | PIC2 FAST ABORT REQ | WAPIC           | PC.UNLOCKED |                 | PIC2 CIRCUIT QUENCH VM           |

| BRCD A13                            |         | PIC2 OPS         | OK       |                    |   |                     |                 |             |                 |                                  |

| RCSA13                              |         | PIC2 CRY         | 0-0K     |                    |   |                     |                 |             |                 |                                  |

| R8.A36                              | (       | PIC1 CIRC        | UIT QUEN | CH VIA QPS         |   |                     |                 |             |                 |                                  |

|                                     | 6:07:12 | 2                |          |                    | 1 | 612:12              |                 | 16:17:12    |                 | 16:22:12                         |

| ٠                                   |         |                  |          |                    |   |                     |                 |             |                 |                                  |

# A centralized framework