lailongwei@sinap.ac.cn

Authors: Longwei Lai\*, Yongbin Leng SSRF, Shanghai, P.R. China

## **·Abstract**

A CW hard X-ray FEL is under construction in SSRF, which pulse rate is designed to 1MHz. A new high-speed sampling BPM signal processor is under development to meet the high performance requirements of beam position measurement system. The processor's sampling rate can be up to 500MHz, and beam position information of each bunch (IMHz rate) can be retrieved with the power of FPGA. Time stamp is aligned with the position data for offline analysis. The processor is designed to be a common signal processing platform for beam diagnostics. The first application is cavity BPM, and other applications, including button BPM, stripline BPM, and even wire scanner processor will be developed based on this platform. At the same time, a RF direct sampling processor is designed for cavity BPM signal processing. This novel technology will greatly simplify the cavity BPM electronic system, and make the system design more efficient and more flexible.

#### Introduction

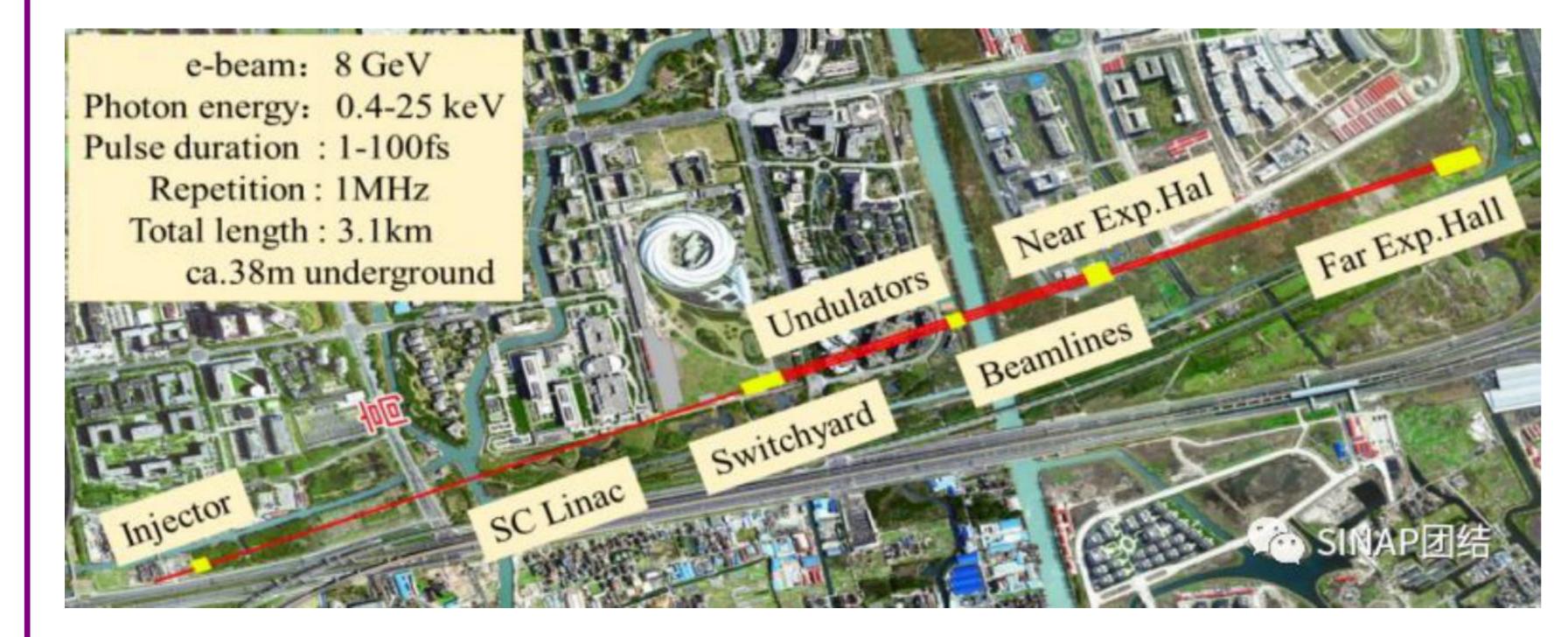

SHINE: Shanghai HI repetition rate XFEL aNd **Extreme light facility.** To be completed in 2025. More than 300 cold button BPMs, stripline BPMs, cavity BPMs on SHINE. A SoC FPGA based standalone beam signal processor platform(DAQ) is under development to meet digital signal processing requirements for all the **BPMs**. The DAQ can process the beam position up to 1 MHz rate.

# •System Overview

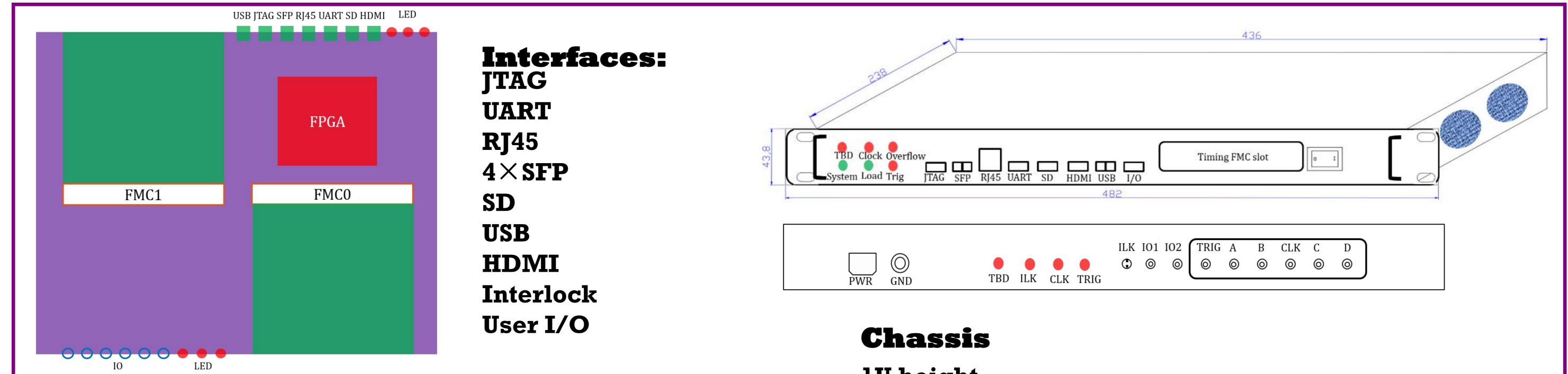

**IU** height 19U width Fans **FMCs open panel** LEDs Easy open

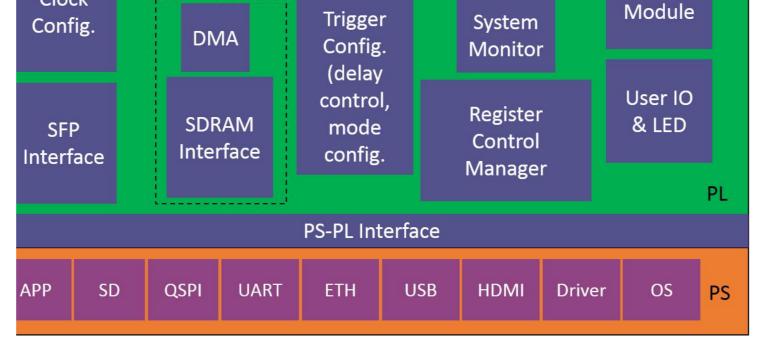

Xilinx Zynq SoC FPGA. **Two FMC interfaces for ADC FMC card and timing** FMC card.

**ADC** card:  $4 \times 500$  MHz/1GHz sampling rate;

≥12 bits; >500 MHz bandwidth ;internal or external sampling clock source.

**Timing card: White Rabbit protocal node; SFP input.**

# FPGA Platform & direct RF-sampling ADC

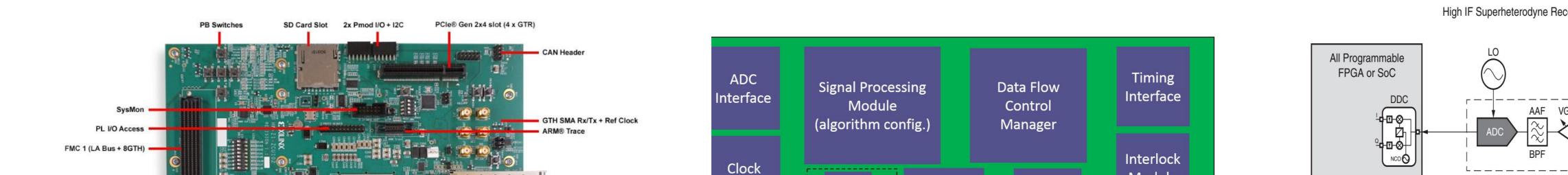

#### High IF Superheterodyne Receiver to a Direct RF-Sampling Receive

### **FPGA** modules overview

Replaced by Integrated Direct RF Subsystem All Programmable RFSoC

**Direct RF-sampling ADCs bandwidth** >5GHz, even up to 9GHz already on the market. Ideal for digitizing of high frequency and narrowband signal, such as cavity BPM signal. **Cavity BPM system structure can be** highly simplified after applying the ADC.

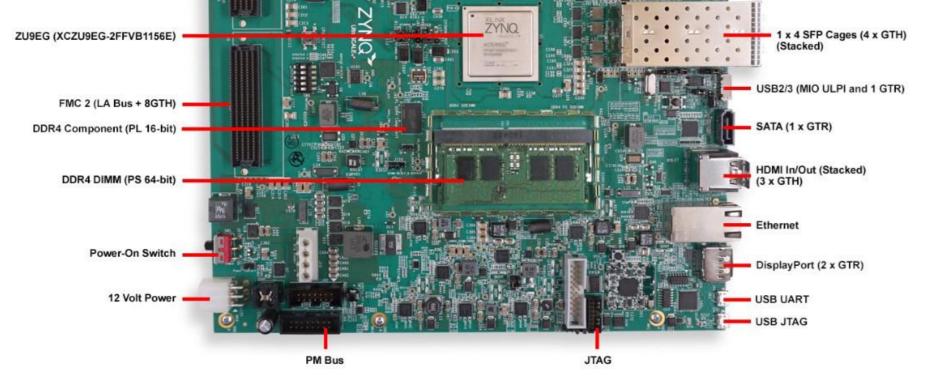

# **FPGA** platform: **ZCU102 Evaluation board:** Zynq UltraScale+ XCZU9EG-2FFVB1156 MPSoC